1、前言

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合,比如电脑的内存条。DDR3 的时序相当复杂,对 DDR3 的读写操作大都借助 IP 核来完成。

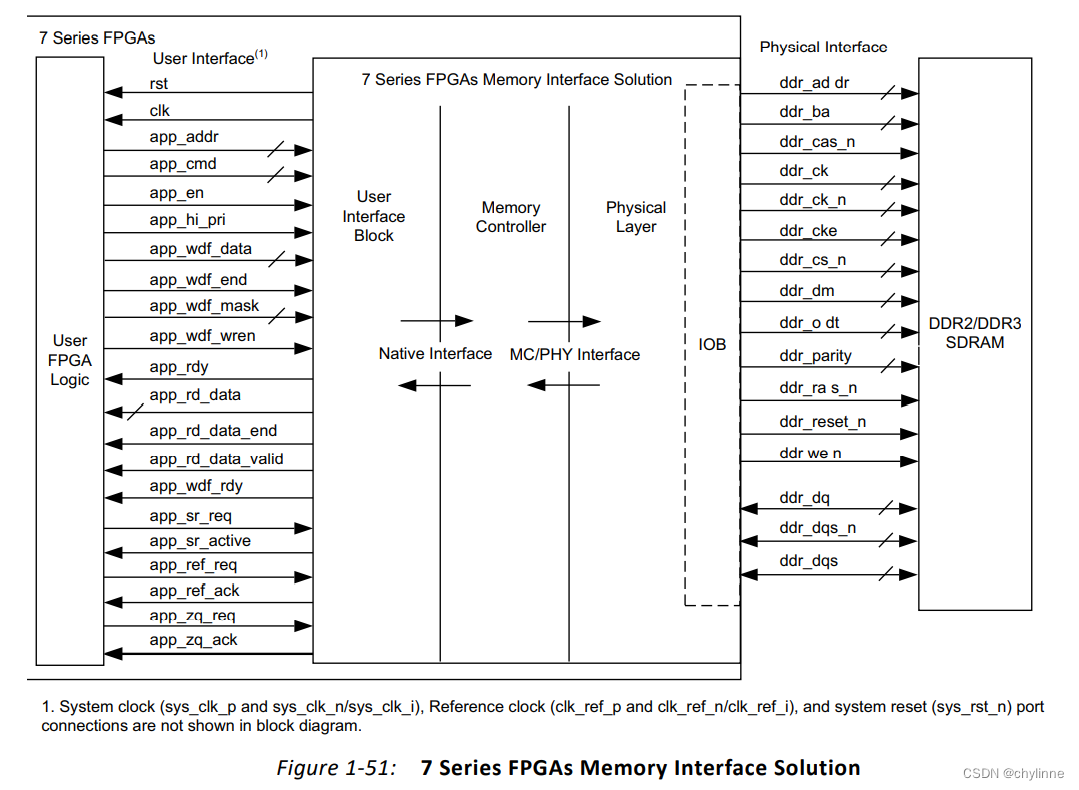

MIG(Memory Interface Generators) IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的 控制流程。在默认情况下,MIG IP 核对外分出两组接口(即 Naive 接口)。一是用户接口,就是用户(FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。二是 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。整体接口架构如下图所示。

本次使用的工程环境为 Xilinx VIVADO 2018.3,工程选择芯片型号为 xc7z035ffg676-2,使用 MIG IP 核默认的自定义(Naive)接口。

2、MIG IP 接口

对于 MIG 与 DDR3 的读写原理我们不需要了解太多,交给 MIG 就可以了。我们需要做的是控制好用户接口,写出正确的用户逻辑,控制好读写时序。下表归纳了每一个用户控制接口的含义。

| 接口名 | 信号方向 | 描述 |

| app_addr | 输入 | 地址总线, UI 聚合外部 SDRAM 的所有地址字段,并提供平面地址空间(rank, bank, row, colum)。这里是读写地址总线复用。根据突发长度 BL= 8,所以地址每次 +8 |

| app_en | 输入 | 命令使能信号,为高时,app_cmd 才有效 |

| app_cmd | 输入 | 命令信号:3’b000:写命令;3’b001:读命令 |

| app_wdf_data | 输入 | 输入数据总线,表示需要写入的数据 |

| app_wdf_wren | 输入 | 写使能信号 |

| app_wdf_end | 输入 | 指示当前周期中 app_wdf_data 总线上的数据是当前请求的最后一个数据 |

| app_wdf_mask | 输入 | 每 1 bit 对应一个输入数据字节,1:屏蔽数据,0:有效数据 |

| app_wdf_rdy | 输出 | 此输出表示写数据 FIFO 已准备好接收数据 |

| app_rdy | 输出 | 此输出表示 DDR 已准备好 |

| app_rd_data | 输出 | 读数据 |

| app_rd_data_valid | 输出 | 输出有效信号 |

| app_rd_data_end | 输出 | 此输出表示当前周期中 app_rd_data 总线上的数据是当前请求的最后一个数据 |

| ui_clk | 输出 | 用户逻辑使用的时钟,取决于在 IP 核中选择的核心频率以及 2:1 或 4:1 模式 |

| ui_clk_sync_rst | 输出 | 复位信号,来自于 IP 核,与 ui_clk 同步 |

| init_calib_complete | 输出 | 表示 DDR 初始化完成,数据才能写入读出 |

| app_ref_req | 输入 | 置 1 时,此高电平有效输入请求内存控制器向 DRAM发送刷新命令。 它必须在一个周期内进行脉冲以发出请求,直到 app_ref_ack 信号被置位以确认请求并指示它已被发送,然后置为无效。一般置 0 |

| app_ref_ack | 输出 | 此高电平有效输入确认刷新请求,并指示该命令已从存储器控制器发送到 PHY |

| app_zq_req | 输入 | 置 1 时,此高电平有效输入请求存储器控制器向 DRAM 发送 ZQ 校准命令。 它必须在一个周期内进行脉冲以发出请求,直到 app_zq_ack 信号被置位以确认请求并指示它已被发送,然后取消置位。一般置 0 |

| app_zq_ack | 输出 | 此高电平有效输入确认 ZQ 校准请求,并指示该命令已从存储器控制器发送到 PHY |

| app_sr_req | 输入 | 保留功能信号,一般置 0 |

| app_sr_active | 输出 | 保留功能响应,不用管 |

3、MIG IP的读写时序

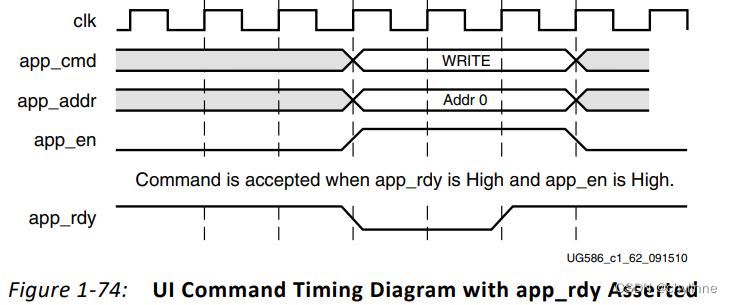

我们从 Xilinx 技术手册中查找写时序的图形如下:

当用户逻辑 app_en 信号有效并且 app_rdy 信号有效时,命令被接受并写入 FIFO。当 app_rdy 被取消置位时,用户逻辑需要将 app_en 保持为高电平以及有效的命令和地址值,直到 app_rdy 有效。

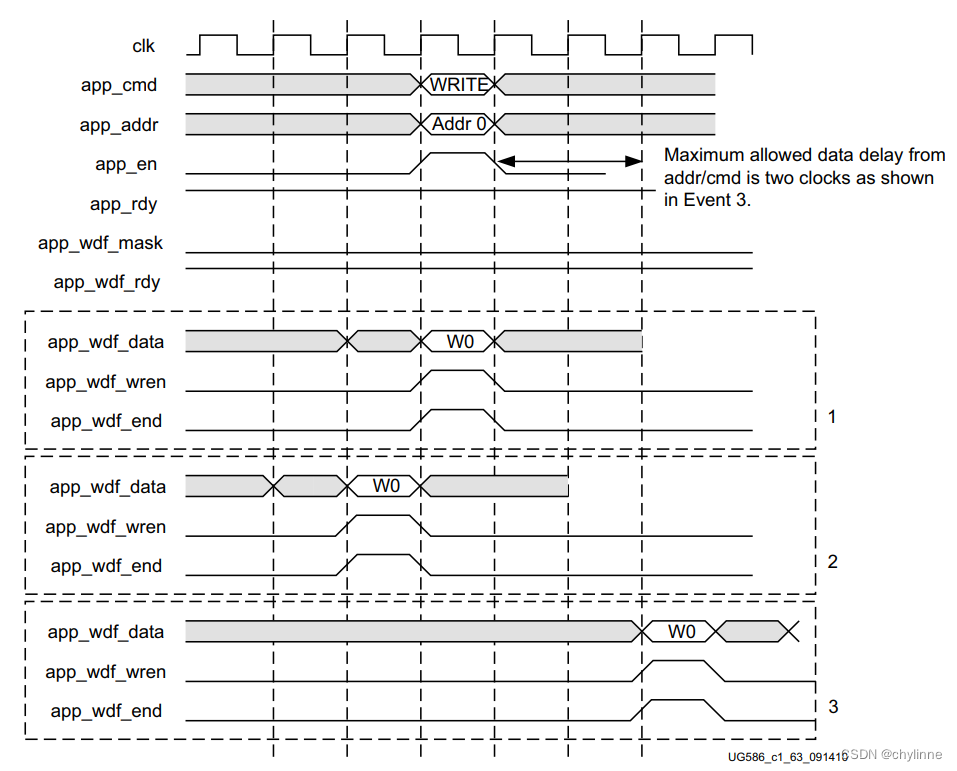

对于写操作,下图描述了 app_wdf_data , app_wdf_wren 和 app_wdf_end 信号的三种场景,这三种场景都是被允许的。

(1)写入数据以及相应的写入命令。

(2)写入数据在相应的写入命令之前。

(3)写入数据在相应的写命令之后,不应超过两个时钟周期的限制。

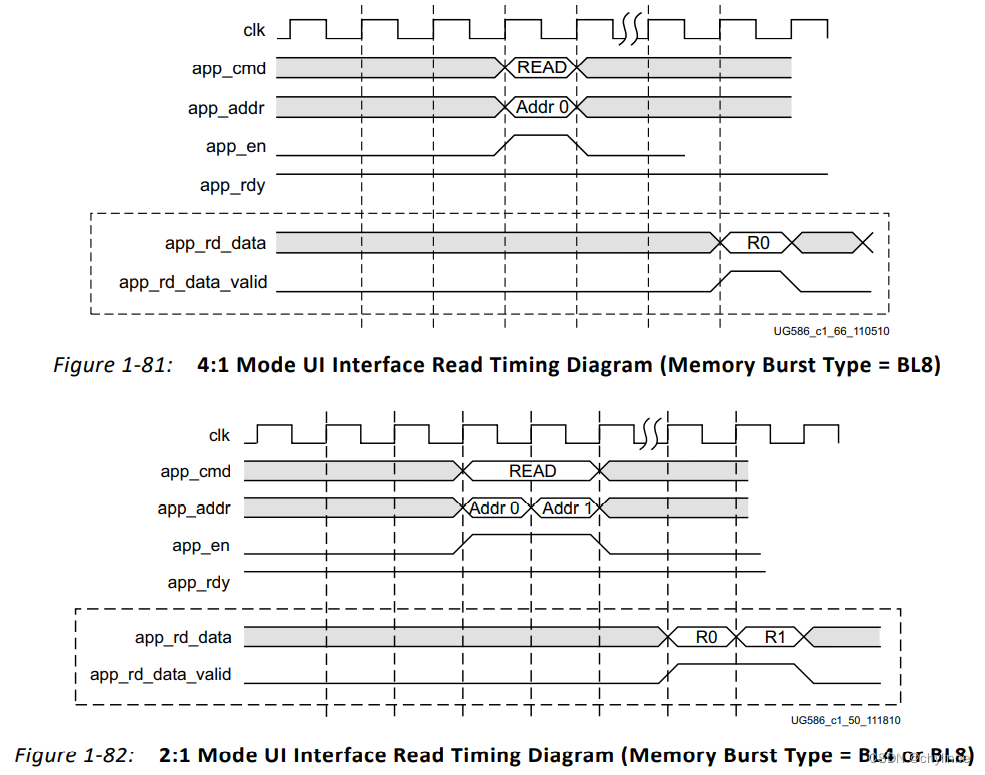

对于读操作,读取的数据由 MIG 以请求的顺序返回,并且在 app_rd_data_valid 有效时数据有效。app_rd_data_end 信号表示每个读命令脉冲串的结束。下图展示了 4:1 和 2:1 两种模式下的读操作时序。

4、MIG IP 核的建立

VIVADO 工程的创建及 IP 核的调用方法,此处直接跳过。

(1)IP 命名与接口选择

打开 IP 核配置界面,首先设置 IP 核名称,此处默认名称为 mig_7series_0。我们本次使用 Naive 接口,因此不勾选最下方红圈所示的 AXI4 Interface。

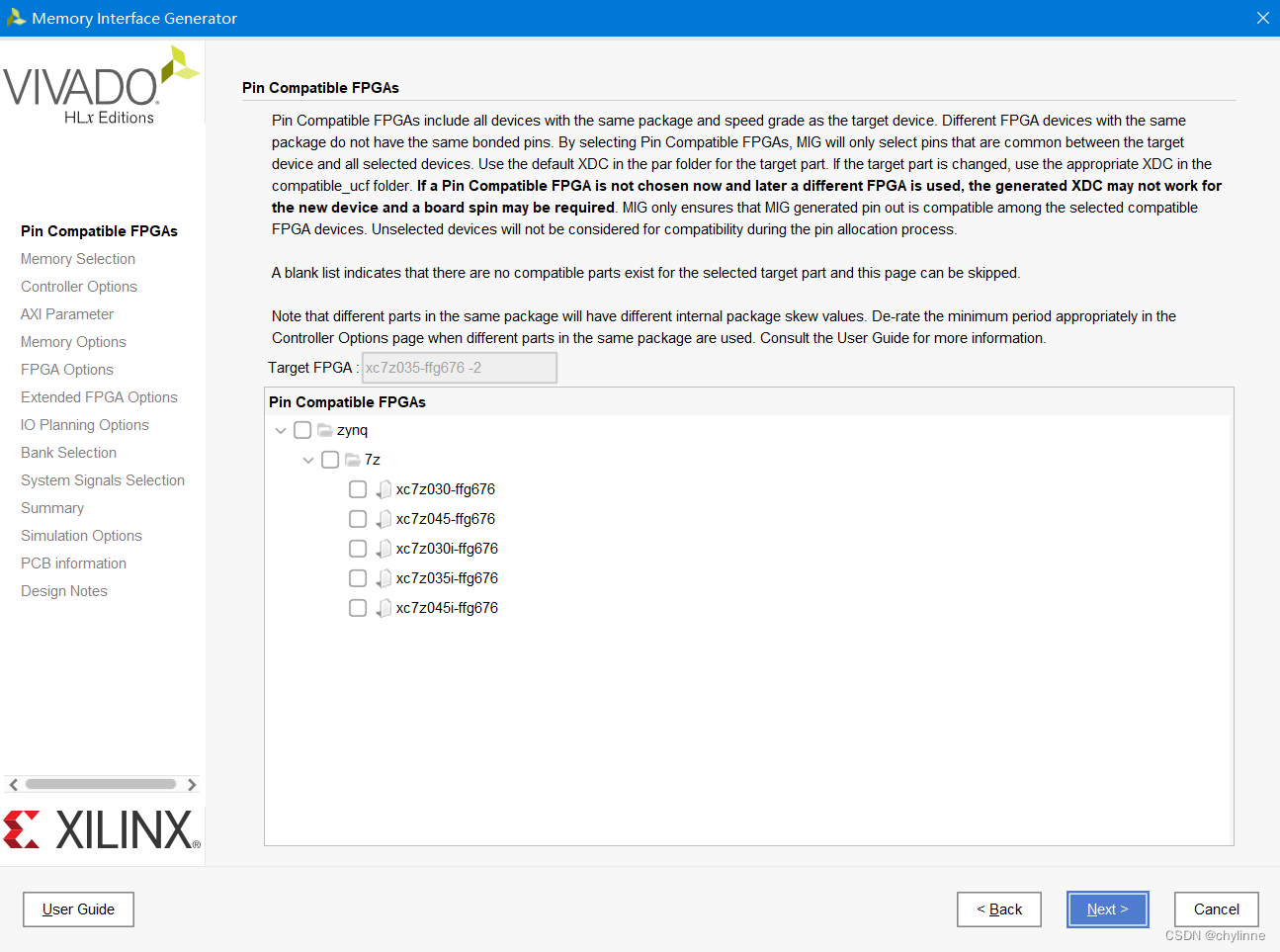

下一页配置该 IP 核兼容的 FPGA 芯片型号,此处无需关心,点击 Next。

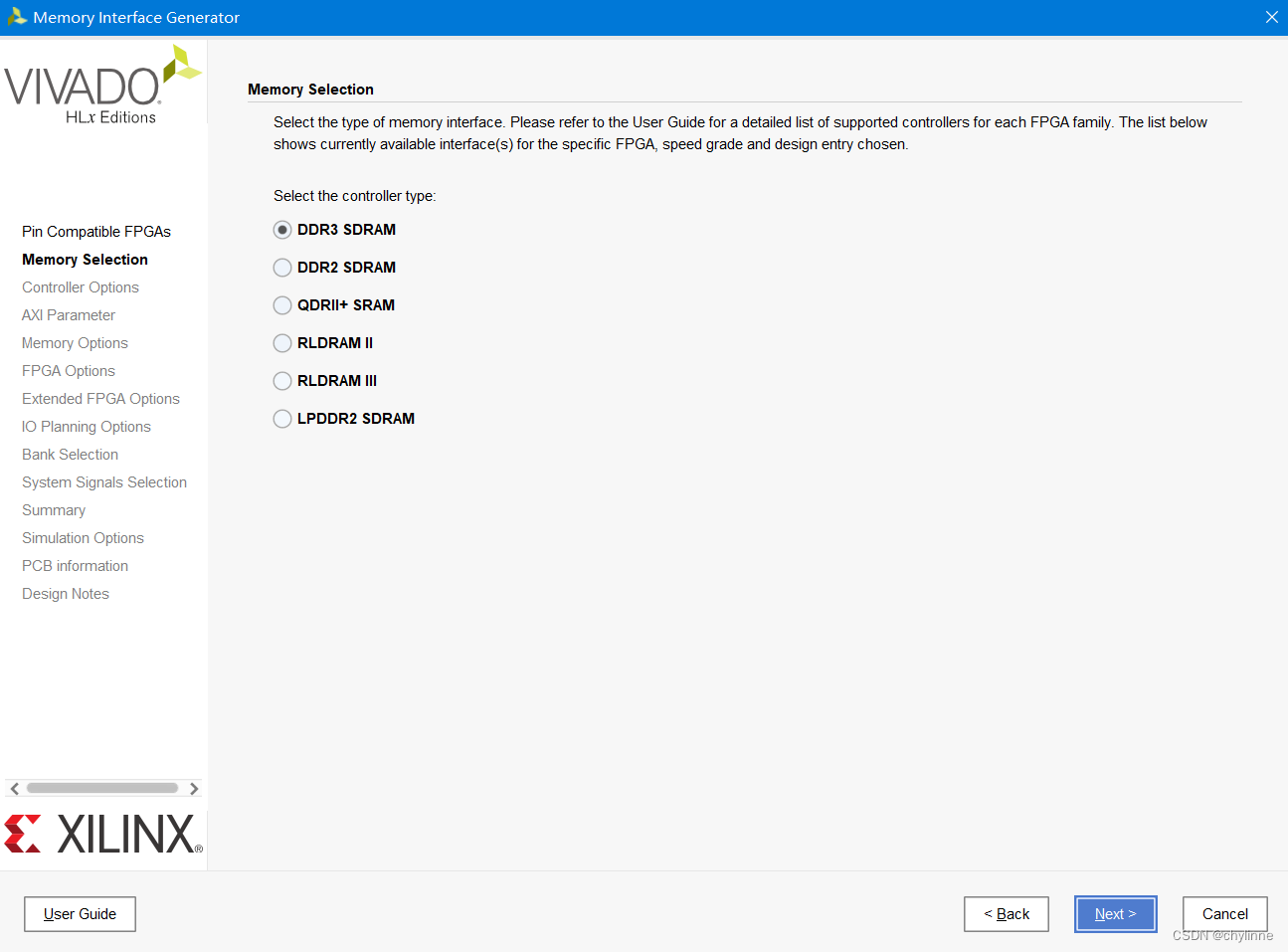

选择 DDR3 SDRAM 模式,也就是该芯片支持的DDR类型,点击 Next。

(2)时钟设置

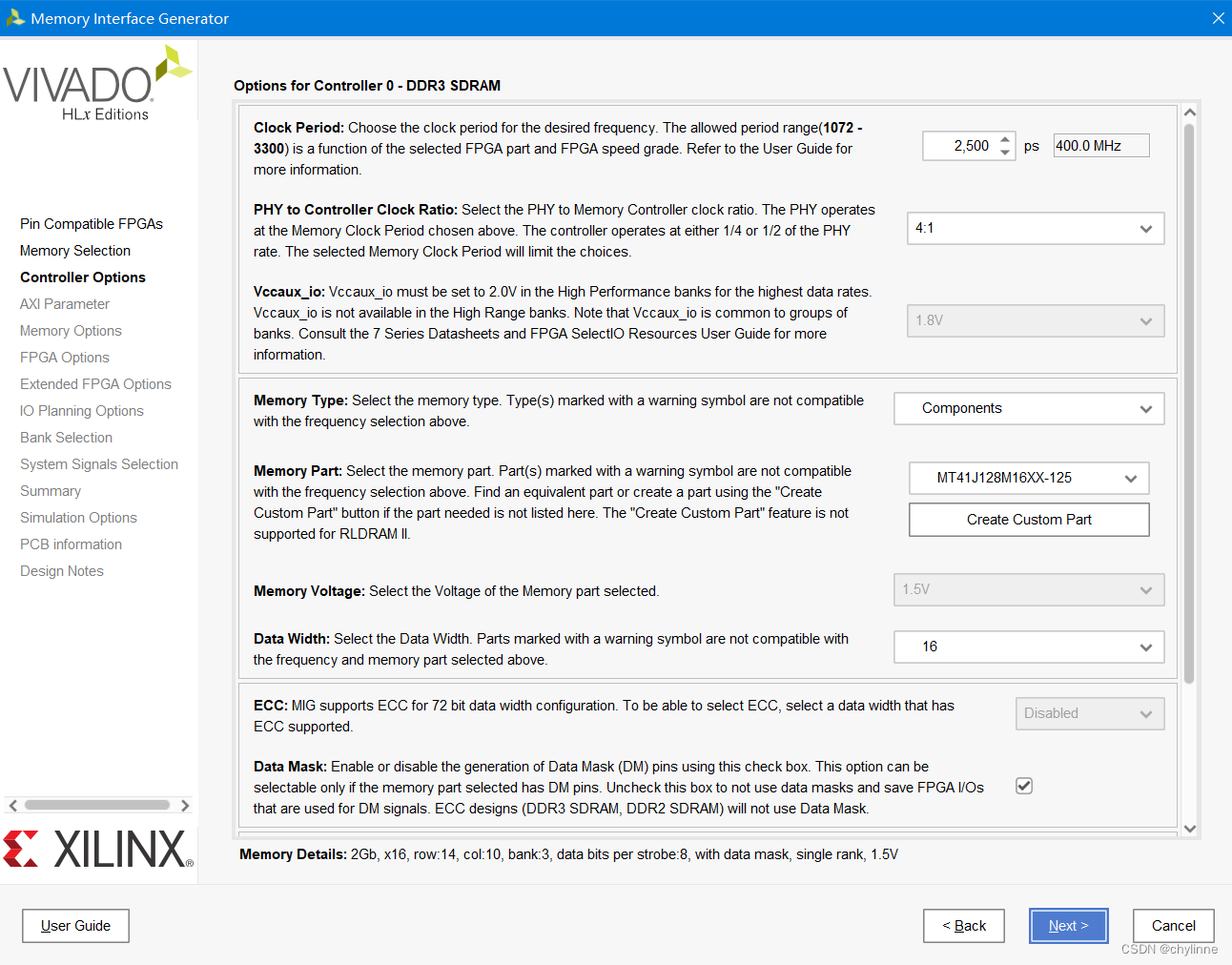

Clock Period 为 DDR3 芯片工作的时钟,这里我们选择 400MHz。控制 DDR 的数据流分为 2:1 或 4:1 两种模式,我们使用 4:1 模式,则 DDR3 的用户读写时钟为 400 ÷ 4 = 100 MHz。

(3)DDR3 芯片型号设置

选择响应的DDR芯片的型号,也可以进行定制,此处我们选择的是 MT41J128M16XX-125。

(4)读写位宽设置

选择 DDR 的数据位宽,这里我们选择 16 位,那么用户实际操作的读写数据为空即为 16 × 8 = 128 比特。

(5)使用数据掩码

Data Mask 处打勾,但实际应用中很少用到掩码功能。

其余的不太重要,就是控制器内部的一些策略问题,详细的可以查看技术手册,点击 Next。

(6)系统(参考)时钟配置

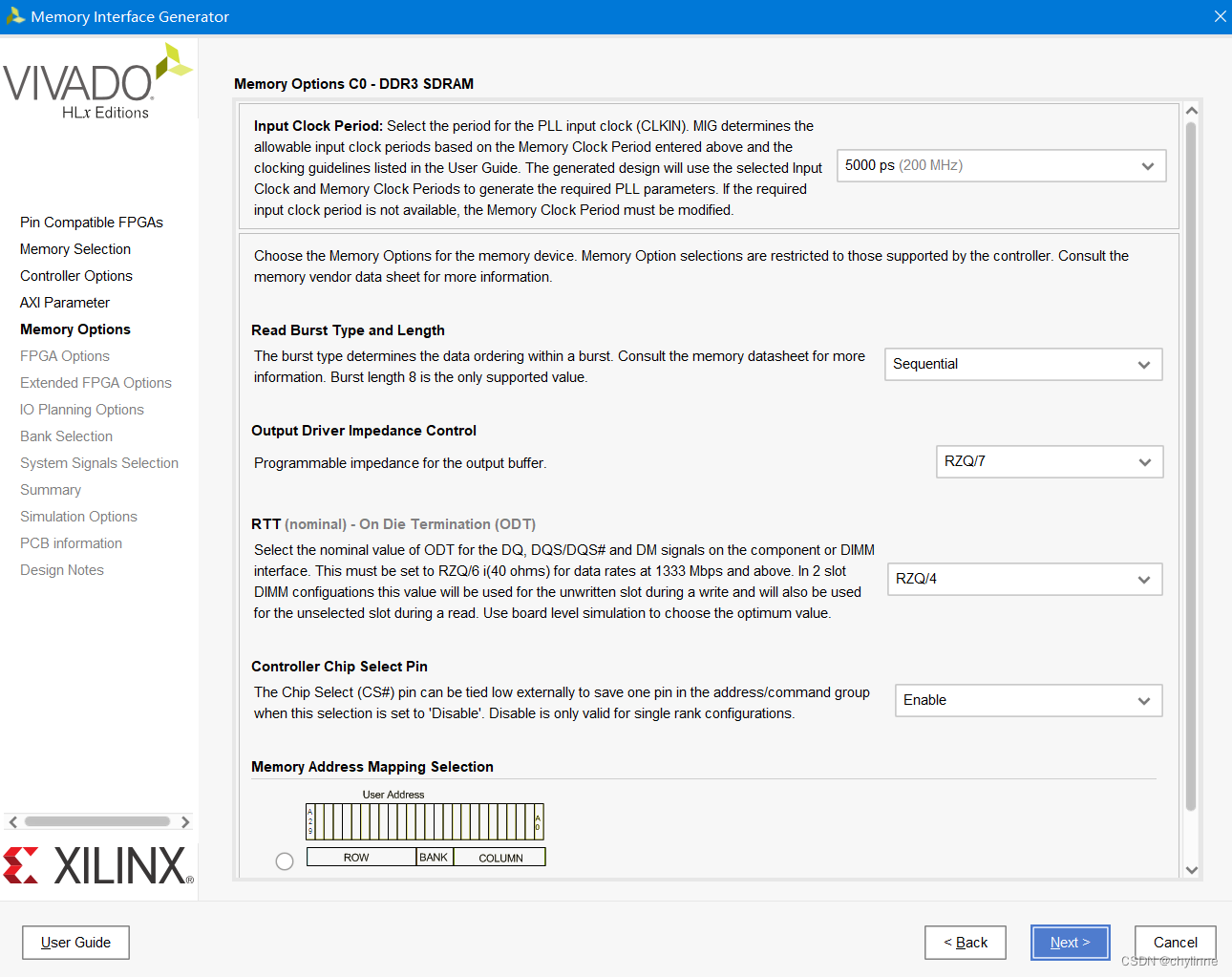

用户提供给 DDR 的系统时钟,用来生成前面 400MHz 的时钟,这里选择 200MHz,因为可以与后面的参考时钟共用一个时钟。

(7)SDRAM 连续模式

SDRAM 有两种模式:连续模式(Sequential)与中断模式(Interleaved),一般选择连续模式。

(8)DDR 寻址模式

即最下方的 Memory Address Mapping Selection,选择用户地址与 DDR3 的实际地址的映射方式,我们选择常用的 BANK-ROW-COLUMN 映射模式。

其余配置均默认,点击 Next。

(9)设置时钟类型

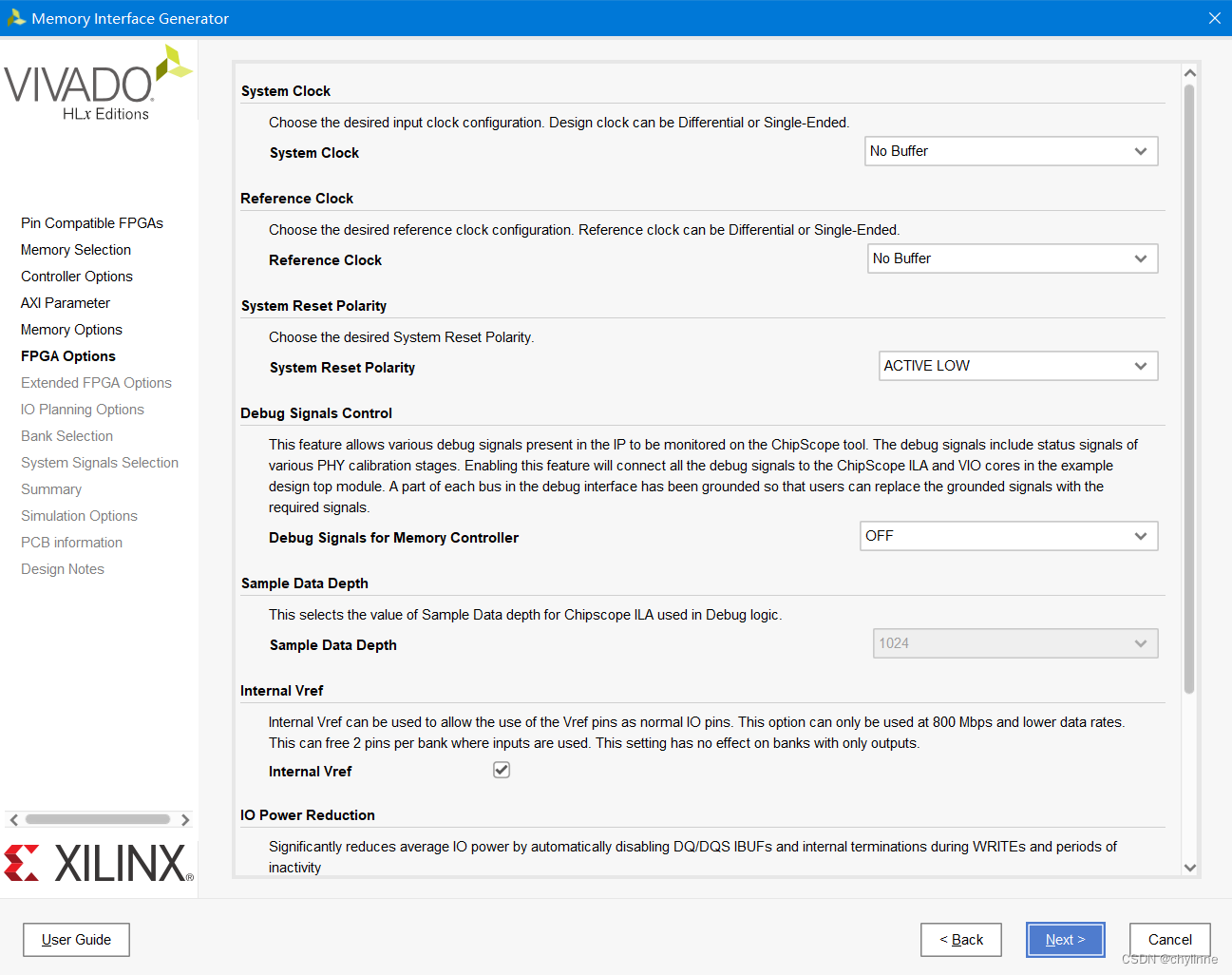

生成时钟的类型,这里面 No Buffer 代表是 FPGA 内部产生的时钟,其余两个是外部时钟引脚直接连接的选项,分别对应着单端与差分时钟信号。这里的 System Clock 和 Reference Clock 我们都使用 No Buffer 模式。其余配置默认即可,点击 Next。

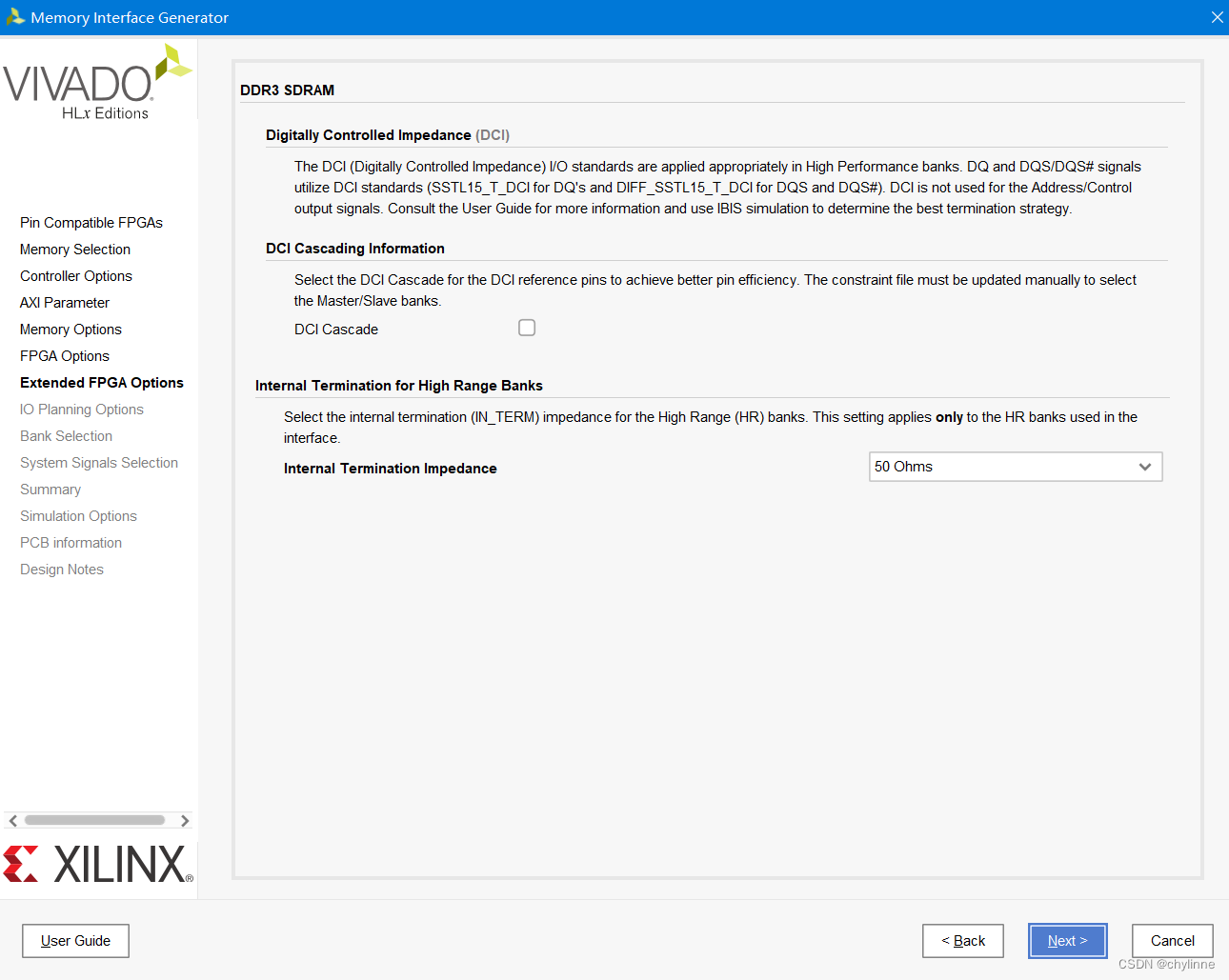

下一页保持默认,点击 Next。

(10)配置引脚

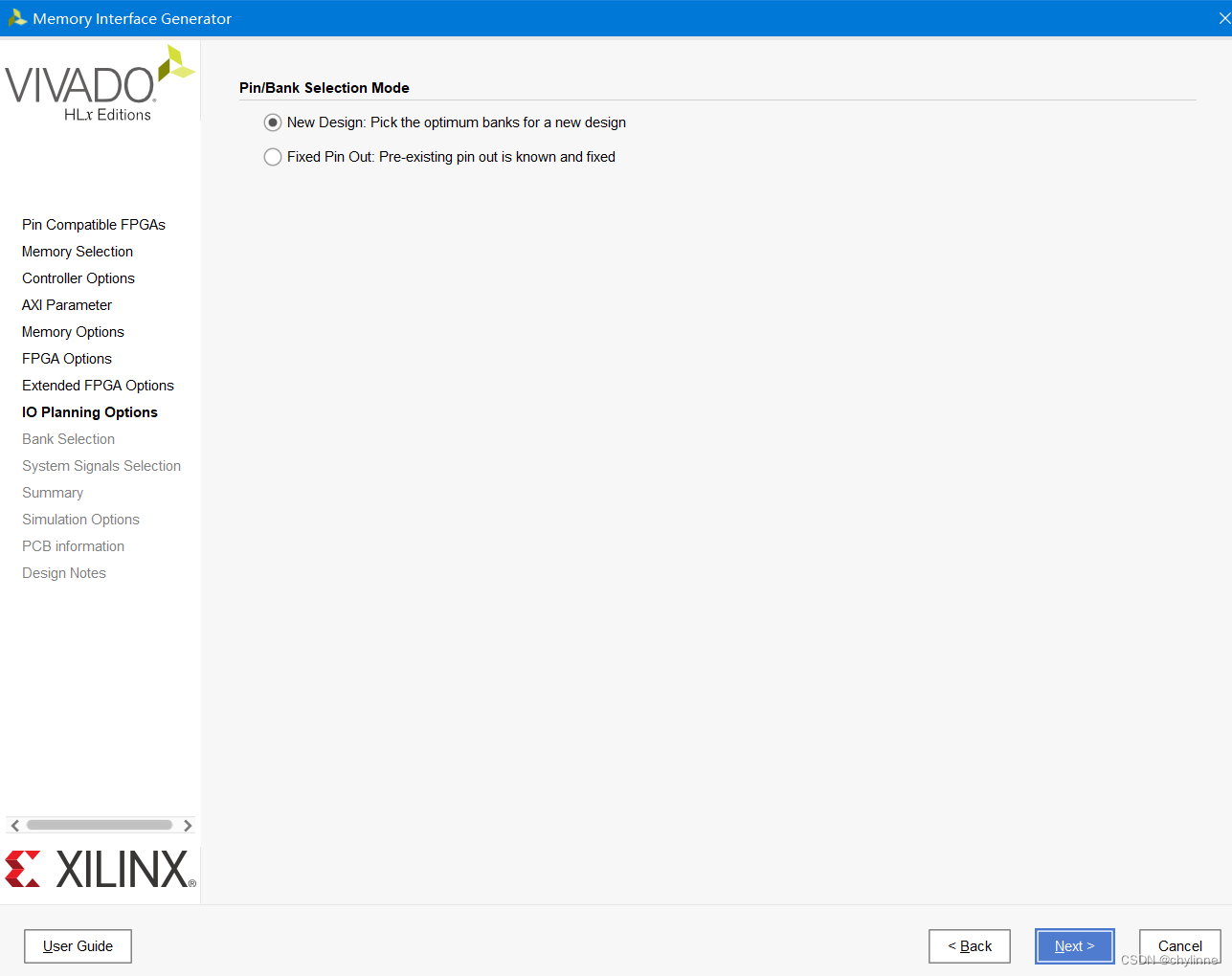

准备根据自己的 FPGA 芯片引脚绑定 DDR3 引脚。我们本次实验可以直接进行如下选择: New Design: Pick the optimum banks for a new design。

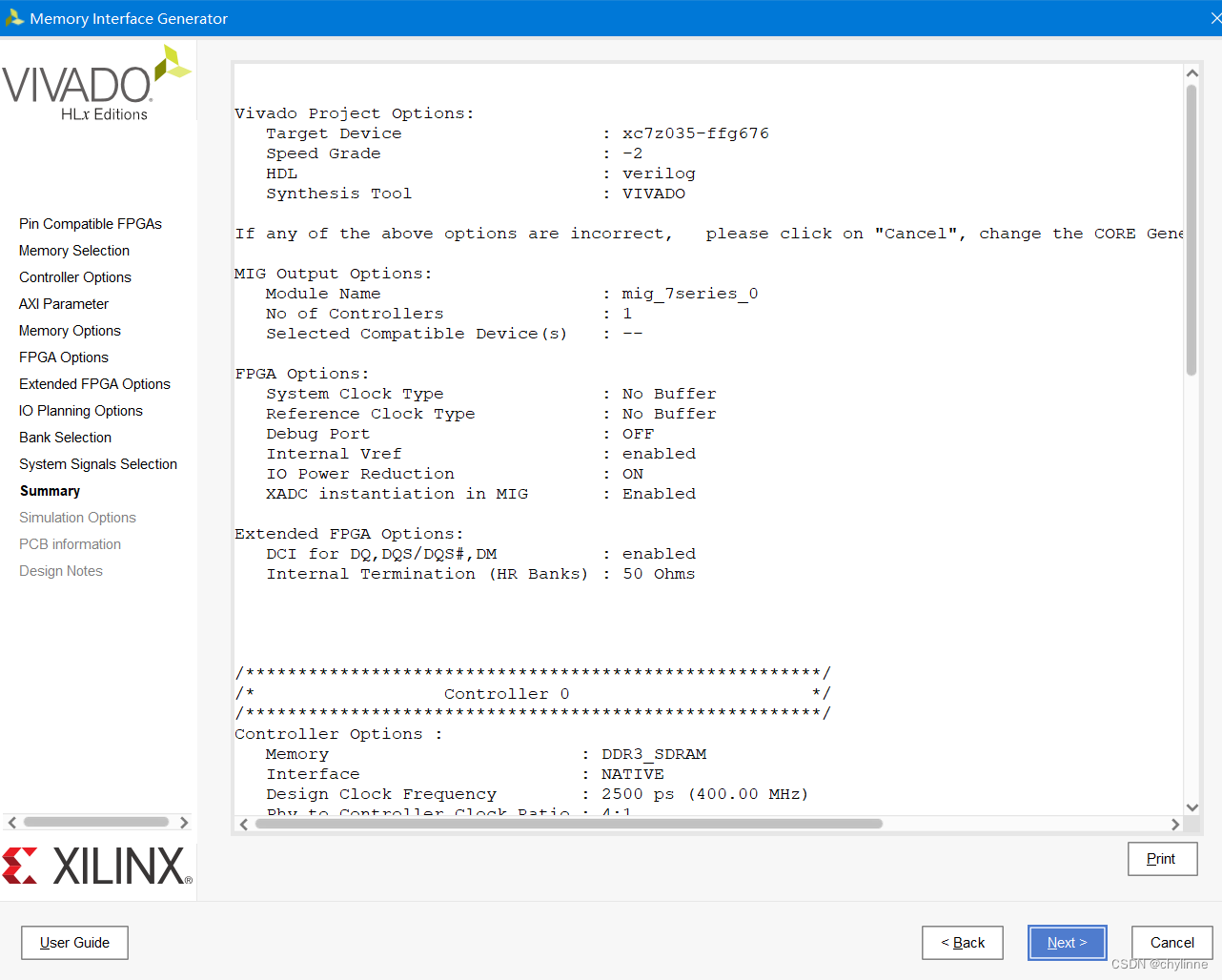

然后是 Summary 页面打印的 IP 核信息,直接点击 Next。

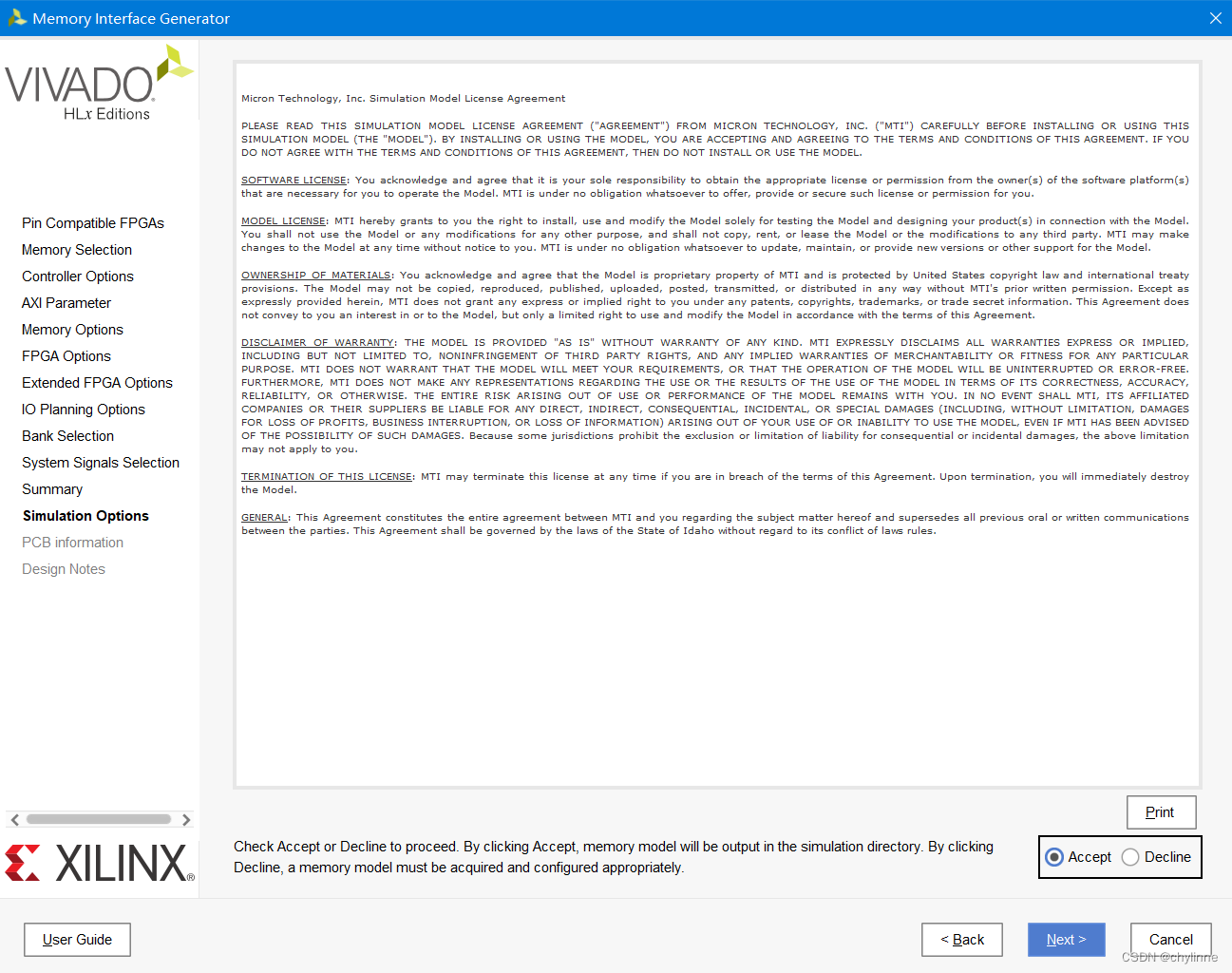

然后是 Simulation Options 页面,选择接受(Accept)协议,点击 Next。

最后一路 Next,生成 MIG IP 核即可。到此为止,我们建立了一个完整新的 MIG IP,并且知道了 MIG IP 核调用过程中每个选项所代表的意义。