版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_46621272/article/details/121396516

FPGA 视频处理 FIFO 的典型应用

FPGA视频处理FIFO的典型应用,视频输入FIFO的作用,视频输出FIFO的作用,视频数据跨时钟域FIFO,视频缩放FIFO的作用 。

摘要

FPGA视频处理FIFO的典型应用,视频输入FIFO的作用,视频输出FIFO的作用,视频数据跨时钟域FIFO,视频缩放FIFO的作用 。提示:写完文章后,目录可以自动生成,如何生成可参考右边的帮助文档

目录

- FPGA 视频处理 FIFO 的典型应用

- 摘要

- 概述

- 一、第一级 FIFO的作用

- 二、第二级 FIFO的作用

- 三、第三级 FIFO的作用

- 四、第四级 FIFO的作用

- 总结

概述

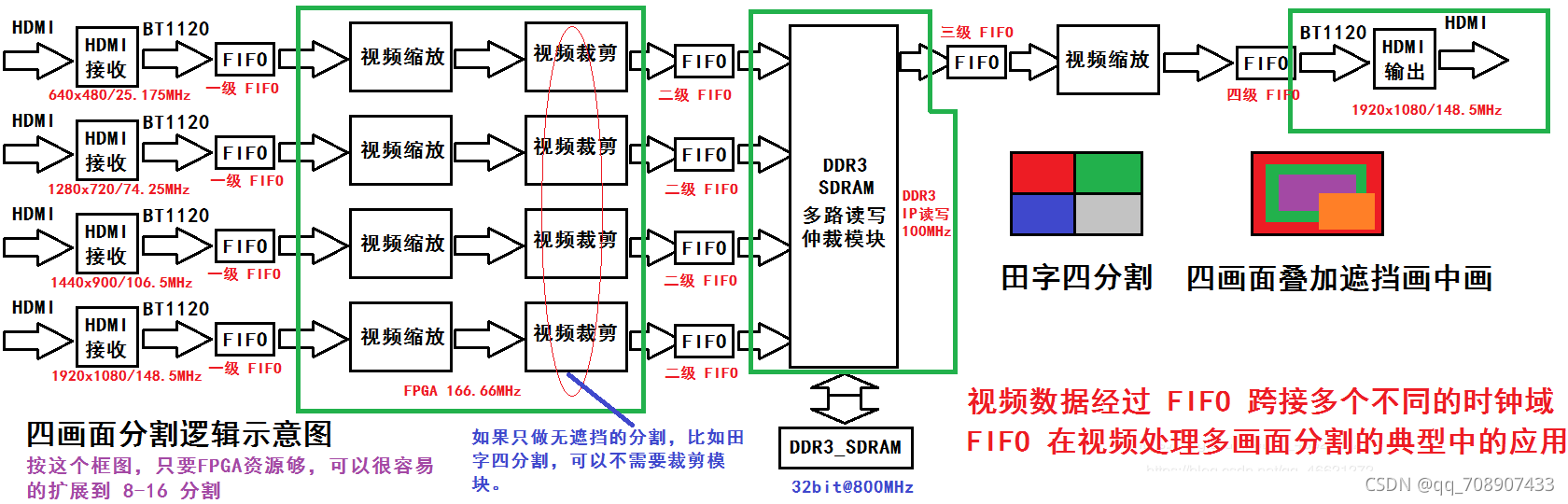

这是一个典型的四画面分割器的FPGA逻辑框图。四个画面能在屏幕内四个任意尺寸任意坐标平铺或遮挡叠加显示四画面分割。在 XILINX ARITX-7 XC7A200TFFV1156 实现,其实在编译是只耗费了不到20%的资源。主要是5路视频(4输入1输出),管脚资源占用太多了。如果采用 Serdes C传输视频(比如视频矩阵板卡),采用 XC7A100 就足够了。

- 在这里我提个问题,大家带着这个问题去看下面的文章,能加深对这图中各 FIFO 的作用。

问题:这图中四级 FIFO 每级 FIFO 满了会出现什么现象?每级 FIFO 空了又会出现什么现象?

一、第一级 FIFO的作用

- 以图为例,阐述第一级 FIFO 三个的作用:

- 隔离时钟域,视频输入的时钟和视频缩放的时钟是不一致的,要完成输入视频的放大(不依赖大容量 DDR3 SDRAM),视频缩放的时钟一定要大于视频输入的时钟,才能正常放大。放大倍数越大,视频缩放的时钟和输入视频时钟比就越大。

- 为视频缩放,特别是视频放大做数据缓存。视频放大后,数据流量就大,就会使视频数据发生短时间的积累。输入口的视频时无等待的,后面视频相关模块的数据处理不过来输入口是不会等的,这就需要一个较大的 FIFO 做数据暂存。

有人这么考虑,视频缩放的时钟如果足够大,是不是可以不用 FIFO 了?是的,但是 FPGA 内部的时钟不能无限大。 在 ARITX-7 用 166.66MHz 做逻辑设计,几乎就是极限了,许多地方的逻辑设计都需要仔细斟酌才能不超时。

以输入视频 640x480 点时钟 25.175MHz 为例,将其放大到 1920x1080 ,

1920x1080)/(640x480)=6.75

理论上需要 25.175*6.75=170MHz 。

实际上,由于输入视频有行消隐场消隐占用了一些无用的带宽,用150MHz + FIFO 就能实现视频的放大。 - 多路视频进 DDR SDRAM 需要仲裁,DDR3 SDRAM 读写效率高,仲裁轮循的间隔就会长,没被仲裁上的视频输入口的数据可不会停,这就需要一个较大的 FIFO 做数据暂存。

这个 FIFO 出现空是好事,说明视频数据顺利的进入 DDR3 SDRAM。

这个 FIFO 是不允许满的,如果这个 FIFP 满了,就意味着后面输入的视频数据会丢失。这是不允许的。

在我的一款产品中,支持的最大输入视频是1920x1080P60 一级 FIFO 是采用 8192x24 容量。

二、第二级 FIFO的作用

- 以图为例,阐述第二级 FIFO 三个的作用:

- 隔离时钟域,视频缩放的时钟(166.66MHz)和 DDR3 IP 读写接口的时钟(100.00MHz)是不一致的。需要用 FIFO 隔离。

- 视频缩放的输出视频流数据 24bit,XILINX ARITX-7 IP 的用户读写接口的位宽是 256bit(DDR3颗粒组用的是32位)。我们采用一个24位像素占用一个32位存储单元的方式存储视频。

最容易实现的是用一个数据宽度比 1:8 的 32位写、256位读的FIFO。

采用这样的 FIFO 对视频缩放后的数据的宽度有要求,需要是 8 的倍数。能满足一些要求不高的应用,比如田字四分割。

我们的设计是自己做逻辑代码,将输入的 24位像素转换成 256位数据写入 DDR3 SDRAM。 - 多路视频访问 DDR3 SDRAM 是需要仲裁的,没被仲裁的视频数据是不能停的,是需要 FIFO 暂存的。这个 FIFO 的大小会影响仲裁的效率,视频路数越多,这个 FIFO 也该调整的大一点。

这个 FIFO 时是允许满的,这个 FIFO 满了后,会影响第一级 FIFO ,使第一级 FIFO 读数据停止,会加速这个 FIFO 变满的过程。

在整体设计中,是不希望这个 FIFO 变满的,最好是一直保持这个 FIFO 不满,只有这个 FIFO 不满才能让第一级 FIFO 不变满。

这个 FIFO 时是允许空的,这个 FIFO 变空,说明该视频流流畅,能顺利的进入 DDR3 SDRAM 。

DDR3 SDRAM 读写仲裁是根据这个 FIFO 的空、满为信号申请仲裁和停止仲裁的。

三、第三级 FIFO的作用

- 以图为例,阐述第三级 FIFO 三个的作用:

- 隔离时钟域,视频缩放的时钟(166.66MHz)和 DDR3 IP 读写接口的时钟(100.00MHz)是不一致的。需要用 FIFO 隔离。

- 视频缩放的输出视频流数据 24bit,XILINX ARITX-7 IP 的用户读写接口的位宽是 256bit(DDR3颗粒组用的是32位)。我们采用一个24位像素占用一个32位存储单元的方式存储视频。

最容易实现的是用一个数据宽度比 8:1 的 256 位写、32 位读的FIFO。我的一款四画面分割器的设计中,就是采用 8:1 的 FIFO 。 - 这个 FIFO 是输出的第一级 FIFO,是需要尽量保持不空的状态。为保持这个 FIFO 不出现空的状态,这个 FIFO 越大越好。

DDR3 SDRAM 读写仲裁是根据这个 FIFO 的空、满为信号申请仲裁和停止仲裁的。

四、第四级 FIFO的作用

- 以图为例,阐述第四级 FIFO 两个的作用:

- 隔离时钟域,视频缩放的时钟(166.66MHz)和 视频输出接口的视频时钟(148.50MHz)是不一致的。需要用 FIFO 隔离。

- 这个 FIFO 是输出的最后一级 FIFO,是不能出现空的状态。为保持这个 FIFO 不出现空的状态,这个 FIFO 越大越好。输出视频时连续的,当这个 FIFO 出现空时,输出的视频就断片了。是不允许的。

总结

第一级 FIFO 不能满,第二级 FIFO 尽量保持不满,第三级 FIFO 尽量保持满,第四级 FIFO 不能空注:在第一节的阐述中,说了输入视频的视频缩放,在不依赖大容量 DDR3 SDRAM 的同时,需要一个较大的 FIFO 和较高的时钟支撑。这个视频缩放是受限制的,是不能将高帧率的小视频放大到1080P。但是在图中输出的视频缩放,这个缩放代码和输入的缩放代码是一样的,未做任何改动。因为缩放前的数据是从 DDR3 SDRAM 读取的,是可控可以暂停的。这个缩放就没有限制了,只要带宽允许,任意尺寸的都能缩放出来。

FPGA 多屏多画面视频拼接器

采用FPGA构建数字视频矩阵的一些设计思路和设计需求

FPGA 四画面视频分割逻辑框图

FPGA 四画面视频拼接单元逻辑框图

FPGA 视频处理中外部SDRAM的作用

FPGA 处理视频SDRAM带宽计算

FPGA 处理视频SDRAM带宽计算(四画面视频分割器)

FPGA 视频处理 FIFO 的典型应用