张士玉小黑屋

一个关注IT技术分享,关注互联网的网站,爱分享网络资源,分享学到的知识,分享生活的乐趣。

当前位置:首页 » 《随便一记》 - 第327页

FPGA:Verilog HDL程序的基本结构

发布 : 游客 | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 353次

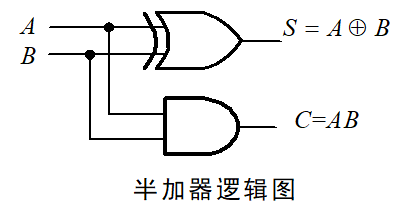

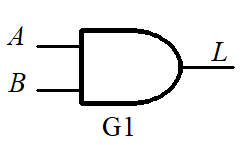

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合VerilogHDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。?本文已收录于FPGA系列专栏:FPGATutorial欢迎订阅,持续更新。?文章和代码已归档至【Github仓库】,需要的朋友们自取。或者关注公-众-号【AIShareLab】,回复FPGA也可获取。简单VerilogHDL程序实例Verilog使用大约100个预定义的关键词定义该语言的结构VerilogHDL程序由模块构成。每个模块的内容都是嵌在两个关键词module和endmodule之间。每个模块实现特定的功能。每个模块先要进行端口的定义,并说明输入(input)、输出(o

【FPGA】Verilog:组合逻辑电路应用 | 数码管 | 8421BCD编码 | 转换七段数码管段码

发布 : 郑州电脑哥 | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 440次

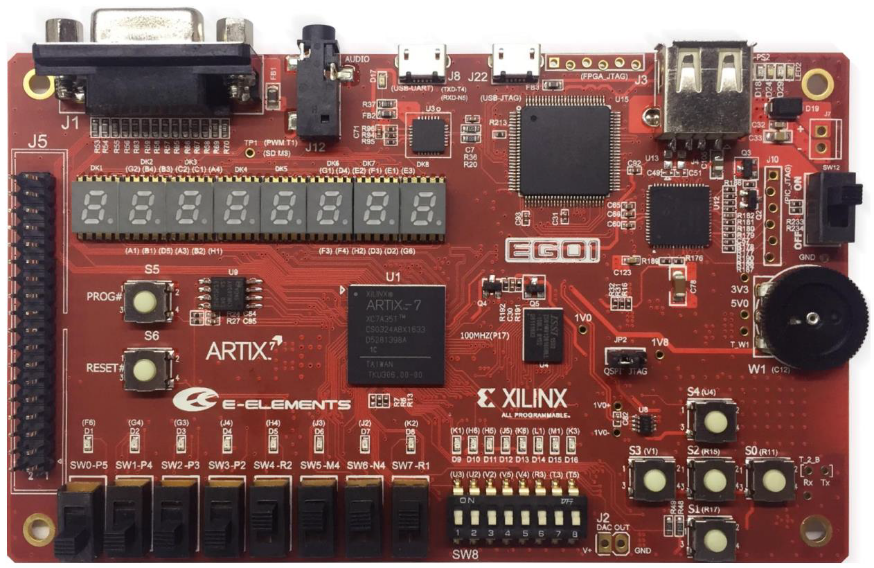

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载示例:数码管的使用功能特性: 采用 XilinxArtix-7XC7A35T芯片 配置方式:USB-JTAG/SPIFlash高达100MHz的内部时钟速度 存储器:2MbitSRAM N25Q064ASPIFlash(样图旧款为N25Q032A)通用IO:Switch:x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin音视频/显示: 7段数码管:x8VGA视频输出接口 Audio音频接口 通信接口:UART:USB转UART Bluetooth:蓝牙模块 模拟接口: DAC:8-bit分辨率 XADC:2路12bit1MspsAD

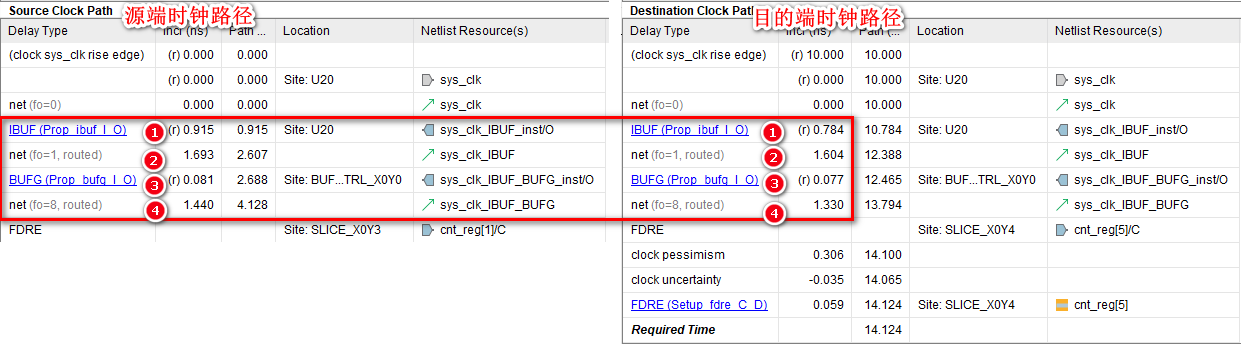

基于Xlinx的时序分析、约束和收敛(8)----关于时序路径、时钟悲观度和建立时间/保持时间的一些问题

发布 : hui | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 431次

Verilog HDL基本语法规则

发布 : 游客 | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 392次

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合VerilogHDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。?文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者公众号【AIShareLab】,回复FPGA也可获取。文章目录词法规定1.间隔符2.注释符3.标识符和关键词逻辑值集合常量及其表示整数型常量实数型常量字符串常量符号常量parameter和localparam区别数据类型(DataTypes)变量的数据类型线网类型变量及其说明关于多重驱动寄存器变量类型寄存器变量类型及其说明memory型变量的用法词法规定为对数字电

module_platform_driver源码分析

发布 : jia | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 334次

在Linux设备驱动开发使用platform平台驱动模型过程中,在定义且初始化好platform_driver结构体变量以后,我们需要向Linux内核注册一个platform驱动,Linuxkernel中有两种方法,源码:include/linux/platform_device.h方式一:/**useamacrotoavoidincludechainingtogetTHIS_MODULE*/#defineplatform_driver_register(drv)\__platform_driver_register(drv,THIS_MODULE)externint__platform_driver_register(struc

三极管从入门到精通

发布 : jia | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 2125次

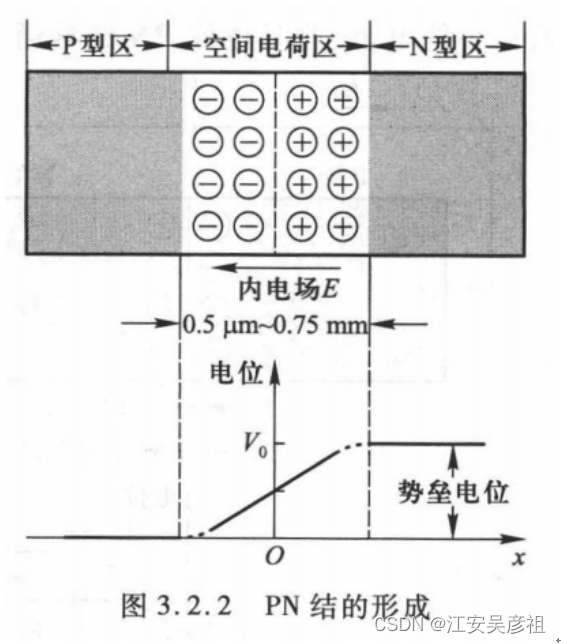

文章目录摘要1基础1.1PN结1.2三极管2三极管模拟电路知识2.1I-V特性曲线2.2极限参数解释2.3基本共射极放大电路2.4小信号模型2.5用小信号模型分析基本共射极放大电路3三极管实际模拟电路应用图3.1共射极放大电路3.1.1基本共射极放大电路3.1.2基极分压式射极偏置电路3.2共集电极放大电路(射极输出器)3.3共基极放大电路3.4各类型电路总结3.5多级放大电路3.5.1共射-共基放大电路:3.5.2共集-共集放大电路3.5.3共源-共基放大电路4最后摘要从PN结开始,介绍了三极管电路符号、物理结构和工作原理,介绍了PNP和NPN三极管的区别及在做电子开关时的用法。针对模拟电路的需要,介绍了三极管的I-V

package.json配置详解

发布 : jia | 分类 : 《随便一记》 | 评论 : 0 | 浏览 : 423次

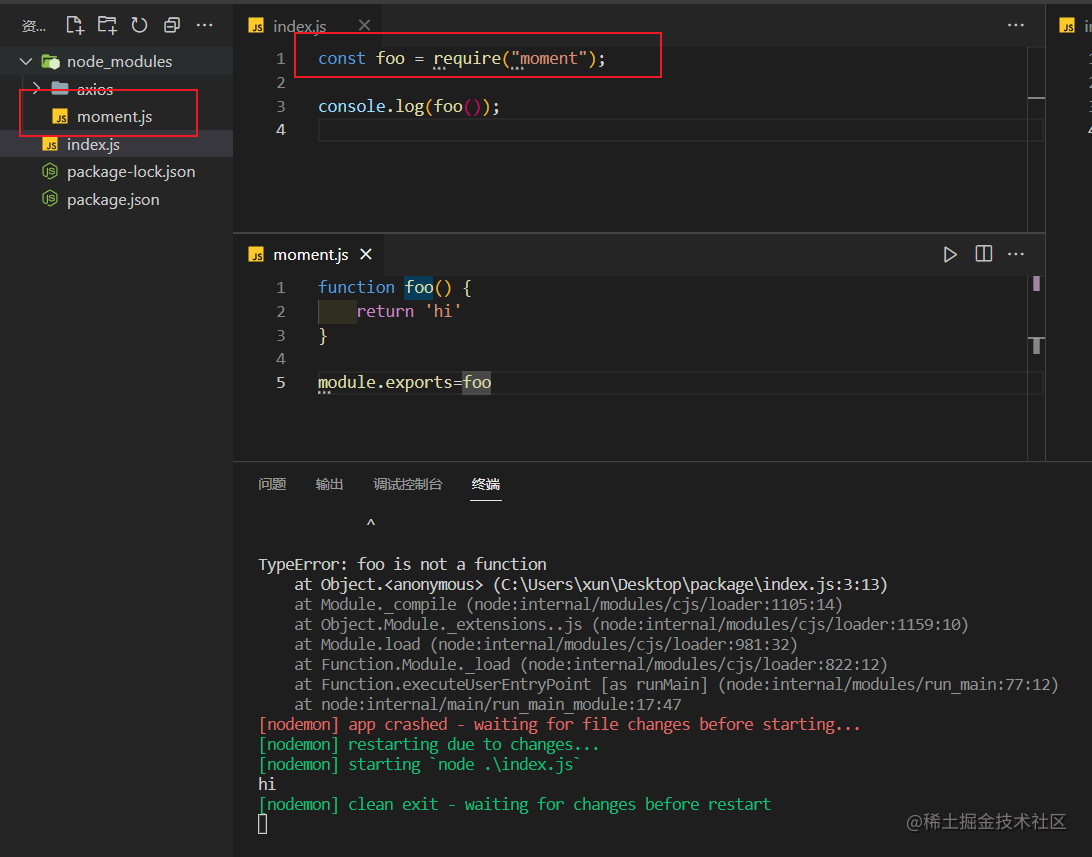

npm介绍npm是随同Node.js一起安装的包管理工具,能解决Node.js代码部署上的很多问题,常见的使用场景有以下几种:允许用户从NPM服务器下载别人编写的第三方包到本地使用;许用户从NPM服务器下载并安装别人编写的命令行程序到本地使用;允许用户将自己编写的包或命令行程序上传到NPM服务器供别人使用;在现在的前端世界里,几乎已经离不开npm了,其提供的依赖安装、卸载、升级、发布等一条龙服务,使我们在日常的开发效率提升了不少。npm制定了一个包规范,所谓规范就是一些格式和约定,比如作为一个npm包中根目录必须包含一个package.json文件,并约定从package.json文件里读取这个包的所有信息,包括它的名字、版本号、它依赖于哪些

search zhannei

最新文章

-

- 她与刺同行快手热门_沈知顾衍赵铭推文_小说后续在线阅读_无删减免费完结_

- 寿命推演,从杂役开始苟到万古无敌精修版_顾长生澹台月好评_小说后续在线阅读_无删减免费完结_

- 云清故事会_云舒小姐太后新上热文_小说后续在线阅读_无删减免费完结_

- 顶流小师妹撕我剧本,他却成了我的裙下之臣好评_沈澈谢谢帅哥最新目录_小说后续在线阅读_无删减免费完结_

- 老公要娶狐狸做平妻,我杀疯了精选作品_陈默老公小少爷精彩分享_小说后续在线阅读_无删减免费完结_

- 婆婆在我婚礼上跳钢管舞热门榜首_林昊婆婆周慧慧无错版_小说后续在线阅读_无删减免费完结_

- 害我入狱,我成狱神后你们连跪都不配!独家番外_陆见秋柳盈盈新上_小说后续在线阅读_无删减免费完结_

- 斗罗v:从逮到千仞雪偷窃开始成神完结版_陈晨胡列娜大反击_小说后续在线阅读_无删减免费完结_

- 末世开火车,顺便捡了个机械神格高分神作_李昂诺亚独家首发_小说后续在线阅读_无删减免费完结_

- 云清免费看_云舒小姐太后校园甜文_小说后续在线阅读_无删减免费完结_

- 军训前,童养媳拿我的病历本给心上人叠纸飞机后,我退婚了完结爽文_杨鹤童养媳阿鹤一口气完结_小说后续在线阅读_无删减免费完结_

- 未婚夫女兄弟把婚车改成宠物灵车,我反手让她的宾利变破烂最新阅读_魏成鸣乔诗诗林书妍小编推荐_小说后续在线阅读_无删减免费完结_

Copyright © 2020-2022 ZhangShiYu.com Rights Reserved.豫ICP备2022013469号-1

![[SSD固态硬盘技术 5] 闪存芯片详解](http://zhangshiyu.com/zb_users/upload/2023/02/20230225094713167728963324744.png)

![[SSD固态硬盘技术 4] 主控详解](http://zhangshiyu.com/zb_users/upload/2023/02/20230225082503167728470355592.png)