目录

1、问题背景

2、存在问题的电路

3、利用CSA改进的电路

4、总结

1、问题背景

在某次电路设计时我需要实现这样的功能:

assign out = (sel ==0) ? c +d : a+ b +d;

因为上述的操作数a/b/c/d都是64bit位宽数据,电路设计时存在串行的两个64bit加法器,最终导致时序无法满足需求(1GHz时钟),经过分析后利用CSA解决了这个问题。

CSA(carry save adder)的原理是在多个数据相加时可以将进位保留下来,只做一次进位传递(具体的CSA细节不在此赘述)。

2、存在问题的电路

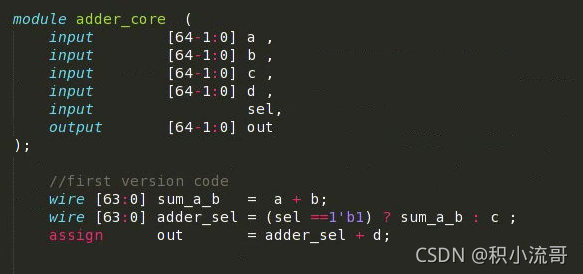

存在问题的RTL代码如下:

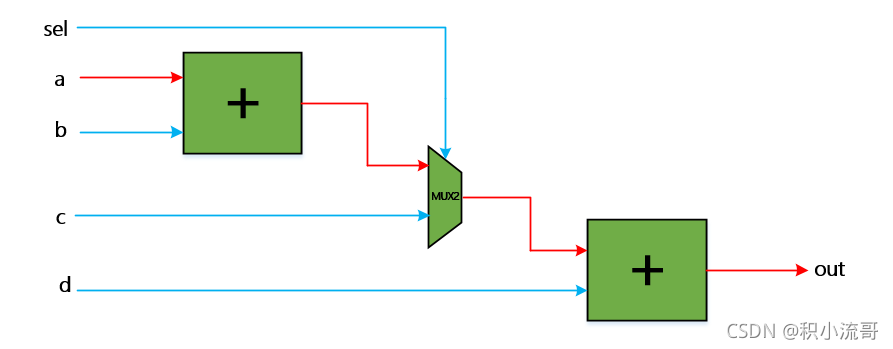

上述代码对应的电路对应下面的图,关键路径用红线画了出来:

可以看到红线穿过了2个64bit加法器,导致延迟过大(无法在1GHz下满足建立保持时间要求)。

3、利用CSA改进的电路

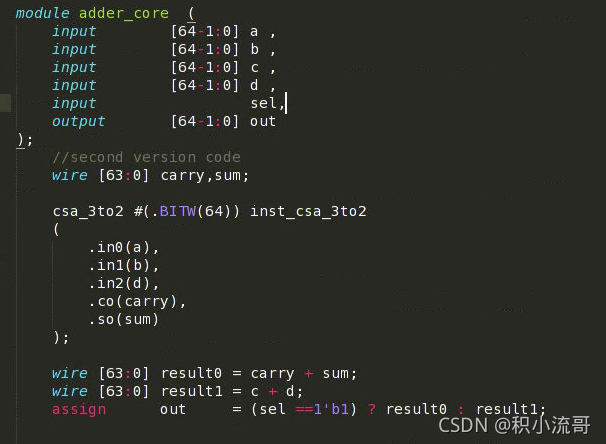

改进后的RTL代码如下:

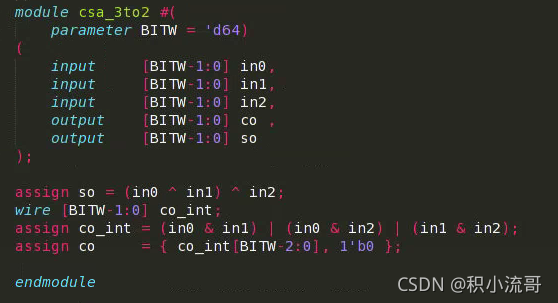

其中csa的代码如下:

可以看到CSA加法器并没有传递进位,延迟仅仅为3个与门(co_int的计算逻辑)。

整体上的电路可以画出如下图,关键路径同样用红色标出:

可以看到原有的2个串行加法器减为1个,有效减少了计算延迟时间(约减为一半时间),消除了违约路径。

4、总结

如果电路设计时存在串行的多个加法器,一般情况下都可以使用CSA优化时序。因为串行的多个加法器实际上存在着进位冗余。例如d=a+b+c,先计算a+b时有一次进位,随后加上c又有一次进位,完全可以合并为一次进位。