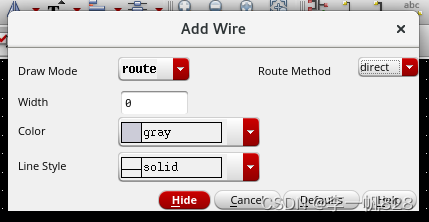

按快捷键w(调用wire)+F3(更改连线属性):显示Add Wire窗口,更改Route Method属性-从full改成direct。

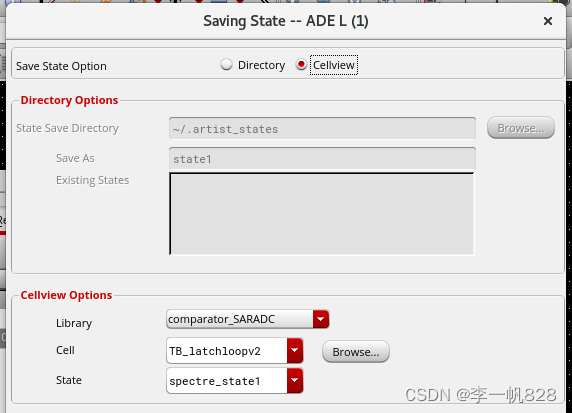

如何将仿真状态保存到cell view?

将仿真窗口ADE L叉掉后,会弹出是否要保存的窗口,选择yes[保存],进而弹出下图所示窗口,选择save state option为【cellview】即可。

virtuoso原理图中label中BUS信号线的使用?

BUS(multi-bits,多比特信号)在数字、数模混合中用的非常多。

1)8-bit的输出信号QB<7:0>连接到负载电容:

①在Name中输入QB<7:0>,

②选中Expand bus names和Attach to multiple wires,

③鼠标单击最左侧导线,自左向右顺次拖动鼠标,就可以看到每个线都标有QB<i>的Label阵列。

在create label对话框的offset输入数字,可以选择label数字的间隔。如输入2,label中的数字就自动依次递增2可以变成a<1>、a<3>、a<5>、.......。

另外通过选择offset后面的升Inc或Dec的按钮,实现label中数字的递增或递减。

2)对输入14-比特信号的MSB补逻辑“1”,LSB补逻辑“0”,构成新的16-比特信号:

①在Name中输入 VDD!, QA<13:0>, VSS! ,

②将生成的Label给attach到“Wide Wire”上。

3)想尝试用一个单线的信号输出给另一条总线的所有子线,即P<8>能否直接连接Q<8:1>?

可以。此时需要将Q<8:1>总线打散。

如何在virtuoso schematic上对某个器件打叉从而禁用这个器件?类似效果见下图。

shift+delete后,点击想要打叉的器件即可。如果想恢复器件的使用,再shift+delete点击就能取消打叉。