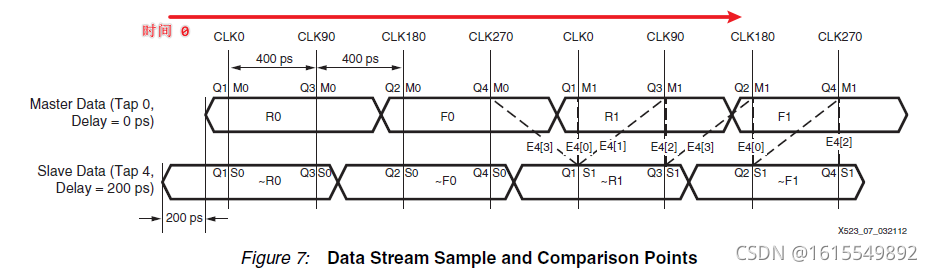

前提:

输入数据是0.5时钟周期变化1次。

图中标记的解释:

Qx [M or S]x

Qx = the ISERDESE2 outputs Q1, Q2, Q3, or Q4

Mx or Sx =Qx的源是Mx还是Sx; the source ISERDESE2 (M = master, S = slave) of the data outputs (Qx)

其中

Q1、Q2中的下标1、2是什么含义?

CLK0 采样的数据下标是1;

CLK90 采样的数据下标是3;

CLK180采样的数据下标是2;

CLK270采样的数据下标是4;

M1、M2中的下标1、2是什么含义?

下标是时钟周期的序号。相同下标表示是同一个周期内的数据。

例如:Q1M1

在CLK0采样Master(没延时45度)的数据输出。