深刻理解GPIO(上拉输入、下拉输入、模拟输入、浮空输入,开漏输出,推挽输出的区别,以STM32为例)_scarecrow_sun的博客

目录

- 前言

- GPIO是什么

- GPIO的八大模式

- 输入模式

- 浮空输入

- 上拉输入

- 下拉输入

- 模拟输入

- 输出模式

- 开漏输出

- 推挽输出

- 复用开漏输出

- 复用推完输出

- GPIO的输出速率

前言

学习了这么久的单片机,说来羞愧,直到写这篇文章之前,我都没有仔细去理解GPIO的八种使用模式,之前只是傻傻的用着,直到把模电,数电学完,到今天重新回顾了一遍这一个知识,发现自己终于看懂了之前没有理解透彻的知识,特此总结下来。

GPIO是什么

从最基础的51单片机,Arduino,到STM32,树莓派等等,这些上面都会有GPIO口这么一个概念,如果你点开了我这个博客,说明你大概率开始学习单片机,那么你应该了解的就是这些口可以输出高低电平,或者是读取引脚上的输入电平。

GPIO的总述功能如下

GPIO(general porpose intputoutput):通用输入输出端口的简称。可以通过软件控制其输出和输入。stm32芯片的GPIO引脚与外部设备连接起来,从而实现与外部通信,控制以及数据采集的功能。

———GPIO简介

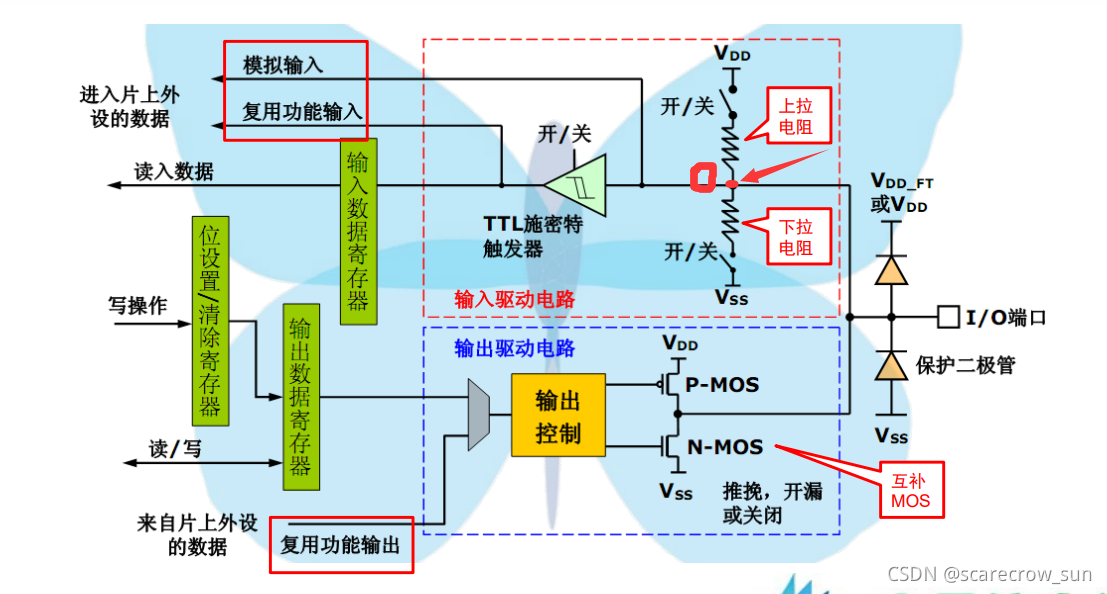

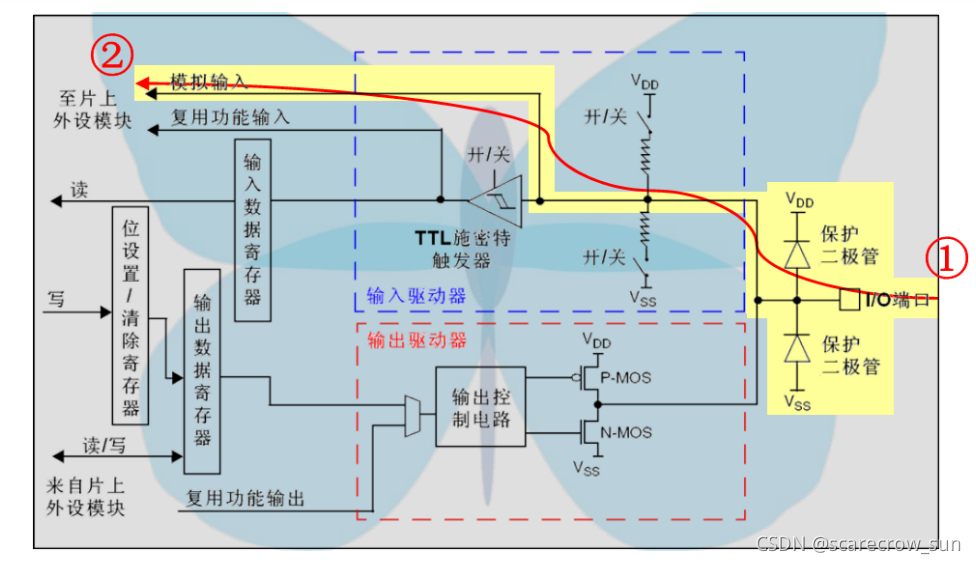

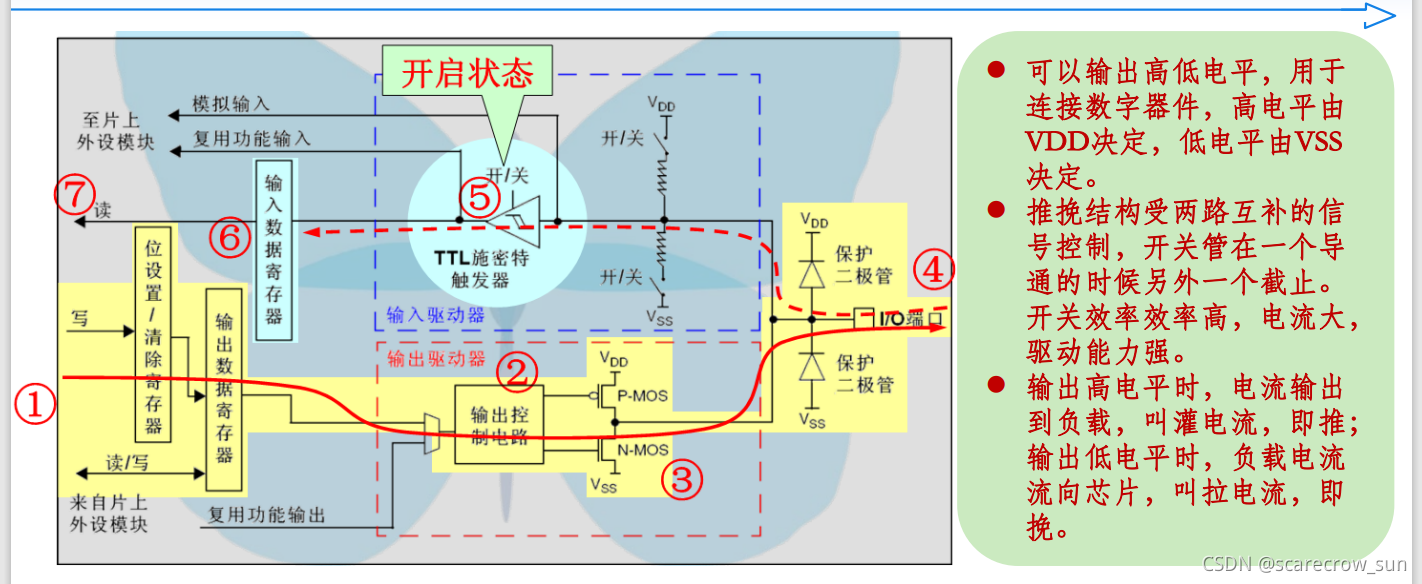

下面摆一张以STM32内部GPIO口为例的内部原理图,大伙也不要着急,先有一个这个图的概念,下面就是开始讲怎么理解GPIO口。

先来一点最基础的知识

上拉和下拉:

当我们打开上拉电阻的开关,关闭下拉电阻的开关的时候,也就是此时为上拉通路导通。根据我们最基础的电路知识,如果I/O口断开不接外设,或者接了外设但是电路也断开,此时整条回路是断路的时候,电阻相当于不存在,此时O点的电位,也就被钳制在了VDD(供电电压正极),于是O点就处于高电平。

同理,打开上拉电阻的开关,关闭下拉电阻的开关,那么在电路断开的时候,根据电路知识,电阻相当于不存在,O点的电压就就被钳制在了VSS(GND),也就是O点处于低电平。

数字信号和模拟信号

数字信号:就是根据一些规则,将一个范围内的电压规定为1,一个范围内的电压规定为0,也就是一连串的0,1信号

模拟信号:就是连续的读取到的电压值。

关于图上的TTL施密特触发器和P-MOS和N-MOS,后面讲到对应部分的时候会讲到。

GPIO的八大模式

GPIO可以分为输入或者输出,加起来一共有八种模式。

输入模式

在输入模式下,一共有四种输出模式,分别是

- 模拟输入

- 上拉输入

- 下拉输入

- 浮空输入

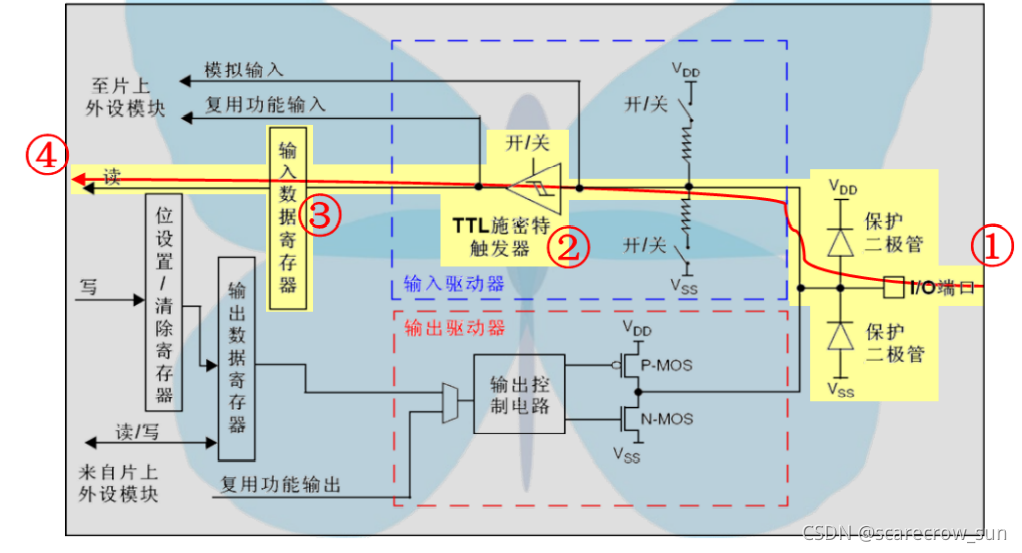

浮空输入

浮空输入需要走的路径如图所示。首先得知道,浮空输出走的这一条路径,是对一个数字信号的读取。

需要的电路如下:

VDD和VSS所在路径的两个开关同时关闭。此时没有上拉和下拉的情况,所以当IO口没有接输入的时候,此时的电平会是一个不确定的值,也就是我们所说的浮空。电平会处于一个跳变的状态,一会高,一会低。只有输入了一个高/低电平才会确定下来。

注意:上拉和下拉电阻电路的开关在实际应用中一般使用MOS管来代替开关来提到。

再往前面走,就是走到了TTL施密特触发器这一个部分。我们知道,由于电源的特性,或者是由于外部开关输入的特性,输入的数字信号,极有可能会出现脉冲等噪声的影响,为了让我们的波形更好看,或者信号更加清晰,所以就设置了TTL施密特触发器这个东西。经过之后,我们就会把这个数字信息存储在输入数据寄存器中。

这样我们就读到了IO过来的数字信号

优势:这一种输入模式的电平会完全取决于外部电路而与内部电路无关。有时候会用作对开关按键的读取。

但是在没有外部电路接入的时候,IO脚浮空会使得电平不确定

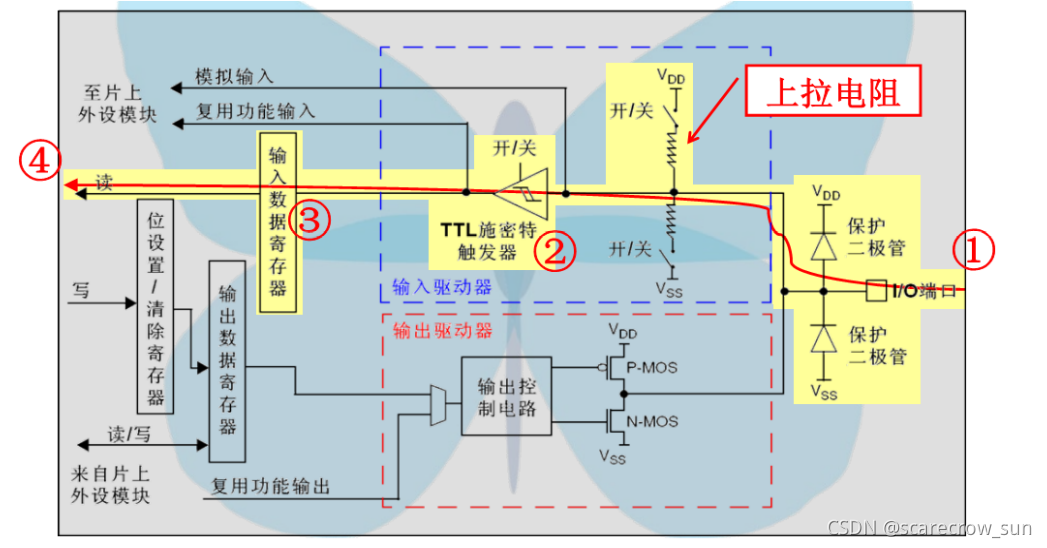

上拉输入

上拉输入需要走的路径如图所示。首先得知道,上拉输出走的这一条路径,是对一个数字信号的读取。

需要的电路如下:

VDD所在上拉电阻开关打开,下拉电阻的开关关闭。

根据前面浮空输入里面所提的,在没有信号输入的时候,根据电路知识,此时的电平就是VDD的电平,此时读取到的电平就是高电平。如果输入了一个高电平,VDD和O点(最上面的图中的O点)之间就几乎没有电势差,此时O点的电平就仍然是高电平,读取到的电平就是高电平。但是由于在没有电压输入的时候,电平也是高电平,所以这一种输入情况下是没有办法确定信号是否输入了。

当输入信号是一个低电平的时候,此时O点的电平的电平就会变成低电平,那么VDD和O点之间形成了电势差,但是因为上拉电阻的存在,所以不会出现一个大电流。此时单片机读取到的一个电平就是一个低电平。在上拉输入的情况下,低电平的是能够非常明显的读取到的。

上拉输入的好处就是输入的电平不会上下浮动而导致输入信号不稳定,在没有信号输入的情况下可以稳定在高电平。

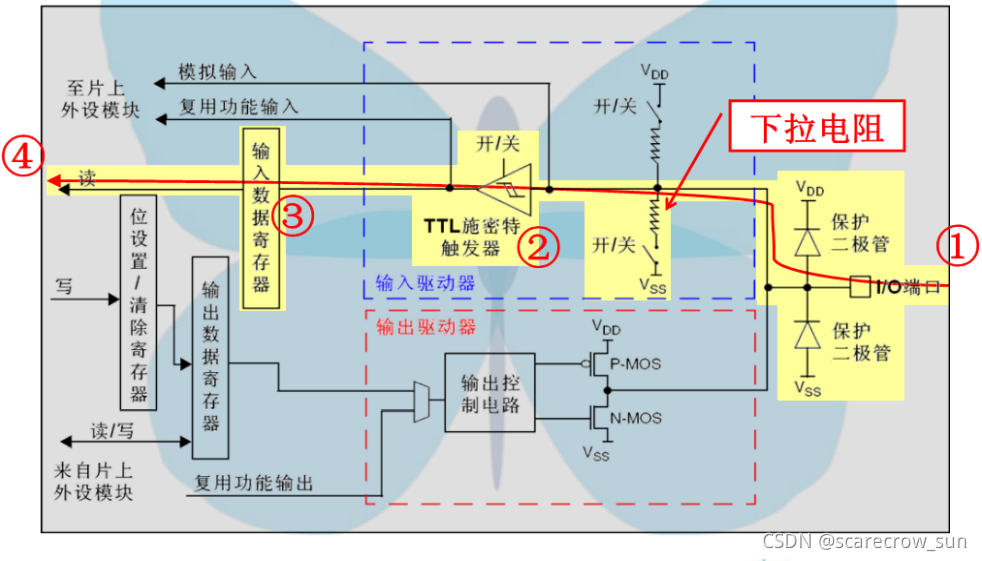

下拉输入

下拉输入需要走的路径如图所示。首先得知道,下拉输出走的这一条路径,是对一个数字信号的读取。

需要的电路如下:

VDD所在上拉电阻开关关闭,下拉电阻的开关打开。

根据前面浮空输入里面所提的,在没有信号输入的时候,根据电路知识,电平就是VSS的电平,此时读取到的电平就是低电平。此时输入的电平如果是一个低电平,就没有办法和之前的情况进行区分。但如果输入的是一个高电平,O点和VSS之间同样形成了电势差,O点的电平会变成外部的高电平,那么单片机得到的就是一个高电平信号。

下拉输入的好处就是输入的电平不会上下浮动而导致输入信号不稳定,在没有信号输入的情况下可以稳定在低电平。

模拟输入

模拟输入需要走的路径如图所示。首先得知道,模拟输出走的这一条路径,是我们需要对一个模拟信号进行读取。

在我们使用单片机的时候,我们有时候需要用AD采集到IO口上面的真实电压。这就有了我们所需要的模拟输入。为了让外部的电压真实的读取到单片机的AD模块,我们既不能打开上拉和下拉的开关,也不能让信号经过施密特触发器。

优势:可以让AD读取电压。还可以在低功耗模式下运行,实现省电的作用。

输出模式

在输出模式下,同样也有四种输出模式,分别是

- 开漏输出

- 推挽输出

- 复用开漏输出

- 复用推挽输出

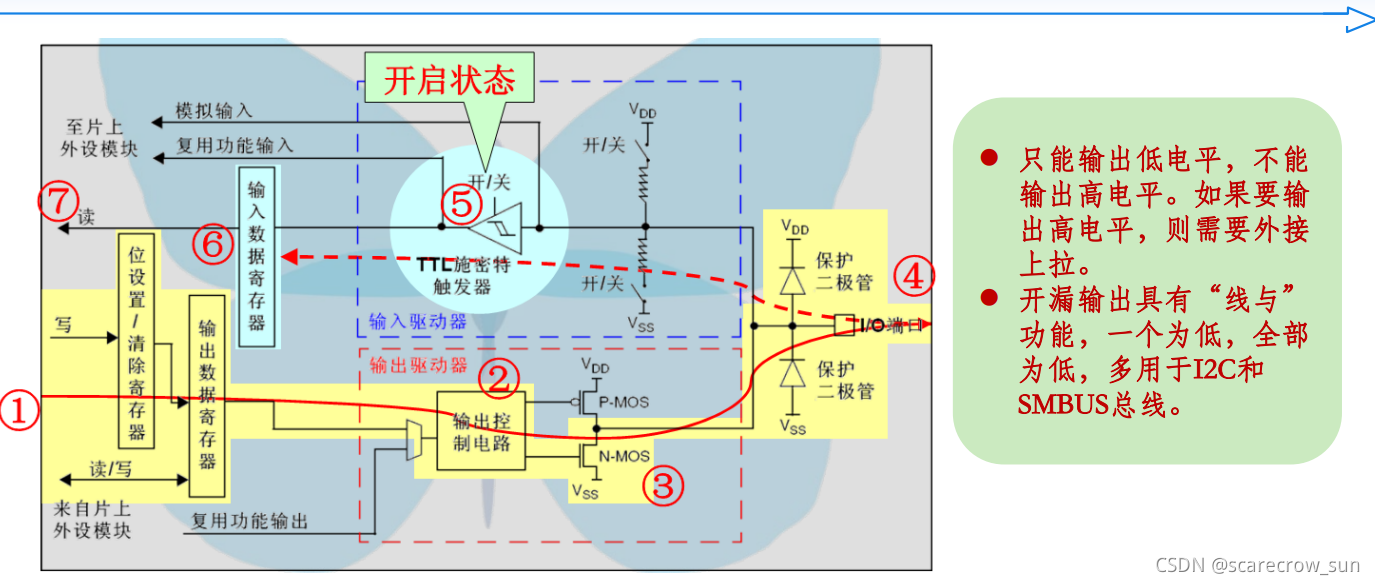

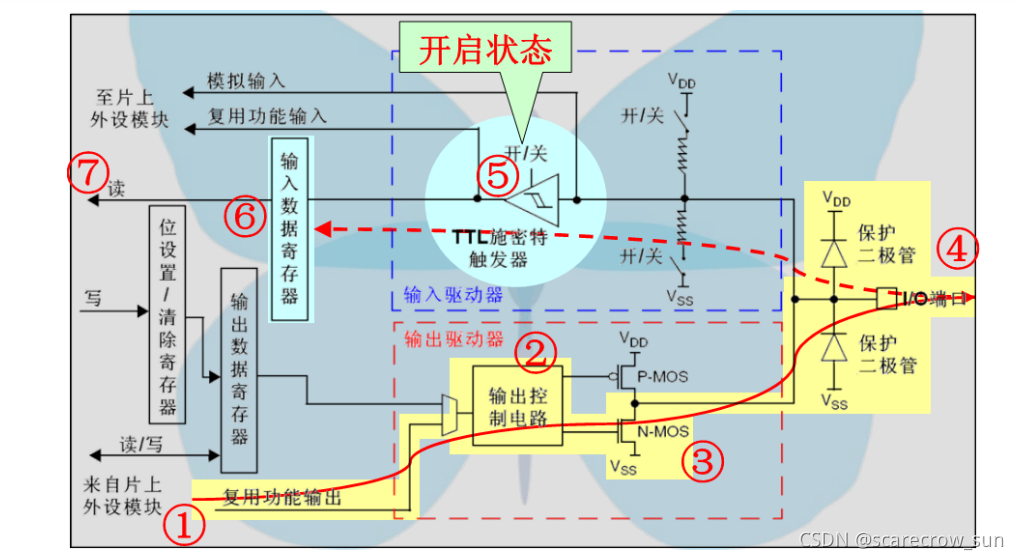

开漏输出

④⑤⑥⑦是读取的过程,此处不管。

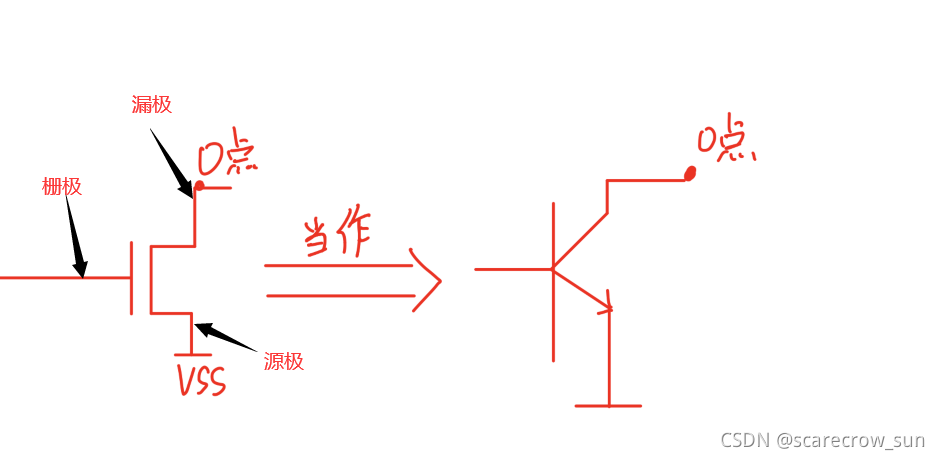

开漏输出的电路路径是①②③④,②前面的步骤就是一个对输出信号的控制,不是重点,开漏输出里面最重要的是③,也就是N-MOS这一部分,下面来补充一下模电知识。

我们可以把这一个MOS管当成一个三极管,对于图中所示的这种三极管我们可以简单的理解成一个水龙头,左侧就是一个水龙头开关,当给一个高电平的时候, O点和GND就会导通。(O点的输出就是一种反向器的输出,也就是O点的电平会和左侧MOS的栅极(三极管的基极)相反)

所以说,开漏输出就很好理解了。当我们给一个低电平的时候,MOS管关闭,此时输出的电压就是一个浮空,即不确定的电压。如果给一个高电平,那么MOS管导通,相当于IO口与VSS相连,此处就输出了一个低电平电压。

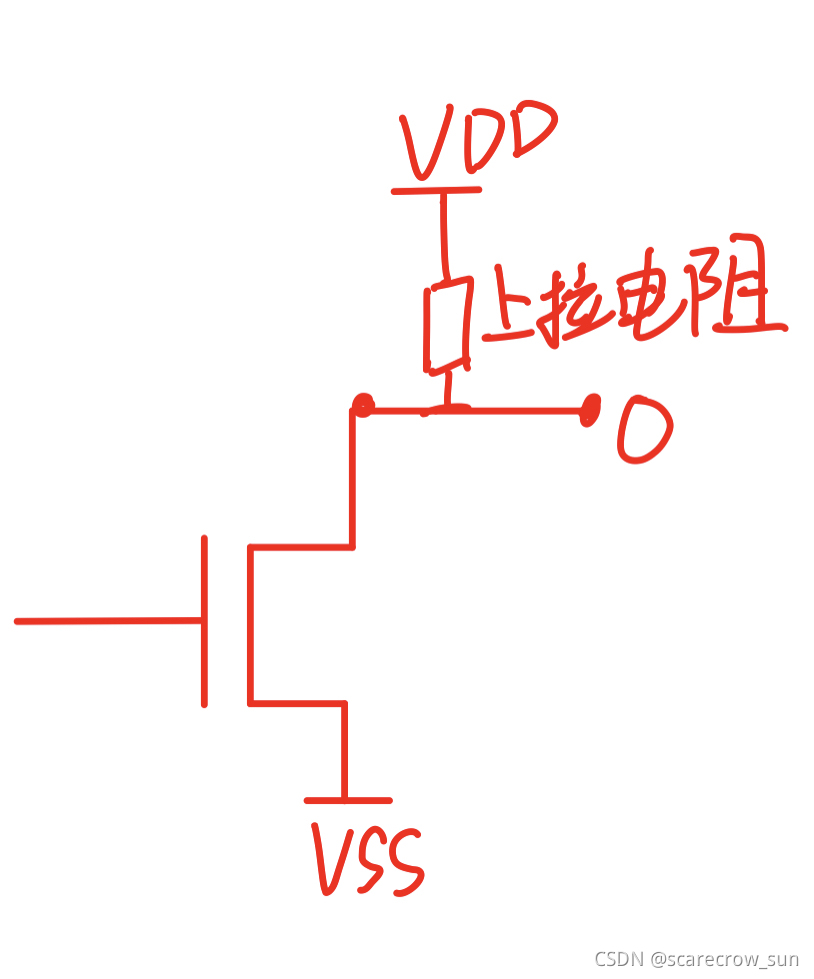

优势①

虽然我们可以看到开漏输出是没有办法在内部输出一个高电平,但是这一个看似是缺点。其实实际上是一种优点。我们可以得到,当给一个低电平的时候,MOS管没有导通,此时电压不确定导致无法输出高电平,但是一旦我们在外部增加一个上拉,那么这一个缺点就会被有效避免。并且,因为是我们自己设计一个上拉,这个上拉的电压是由我们自己确定,这样我们就可以根据外部电路需要多少V的高电平来给这一个上拉的电压,可以更好的适应更多情况。如下图,我们可以给定任意的VDD电压,来适应我们实际所需要的情况。

优势②

开漏输出的实质其实就是一个OD门(OD:漏极输出(Open Drain))。而在数电中,OD门有一个非常重要的特性就是可以实现线与的功能,简单来说,就是在像IIC这样的总线协议中,只要有一个给低电平,那么总线都会被拉低。

推挽输出

推挽输出就是可以需要利用两个不同的MOS管来实现输出。

P-MOS和N-MOS是不同的控制方式,当给一个高电平的时候,N-MOS导通,P-MOS不导通,此时IO口接通在VSS,此时输出的是低电平。当给一个低电平的时候,P-MOS导通,N-MOS导通,此时IO口接通在VDD电源上面,此时输出的是高电平。

一定要把这个MOS管理解成开关控制的水龙头!!!

优势

带载能力强。

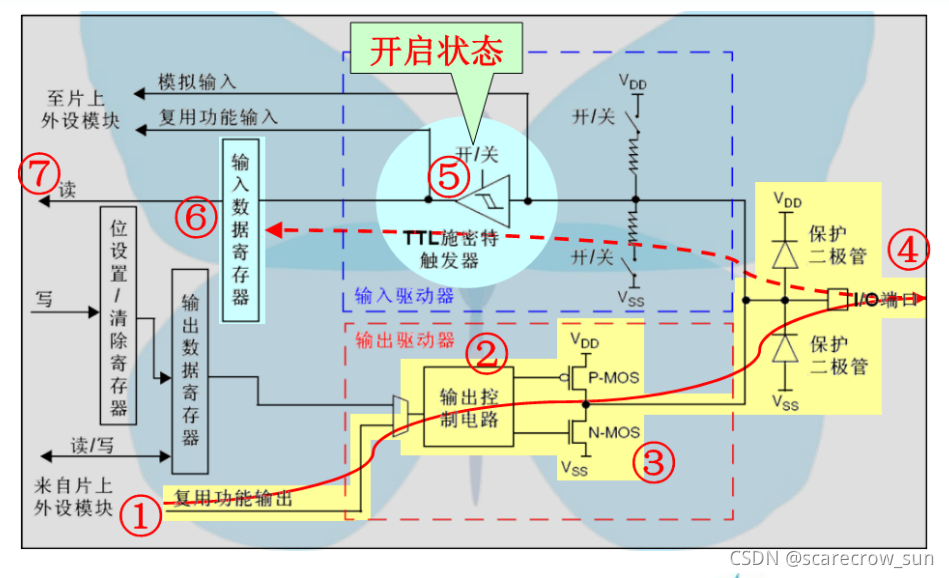

复用开漏输出

复用推挽和复用开漏其实很简单,在你理解了开漏和推挽的原理之后,如果你不想用单片机内部来输出,那么你可以进行复用,将输出转移到其他外设上面

复用推完输出

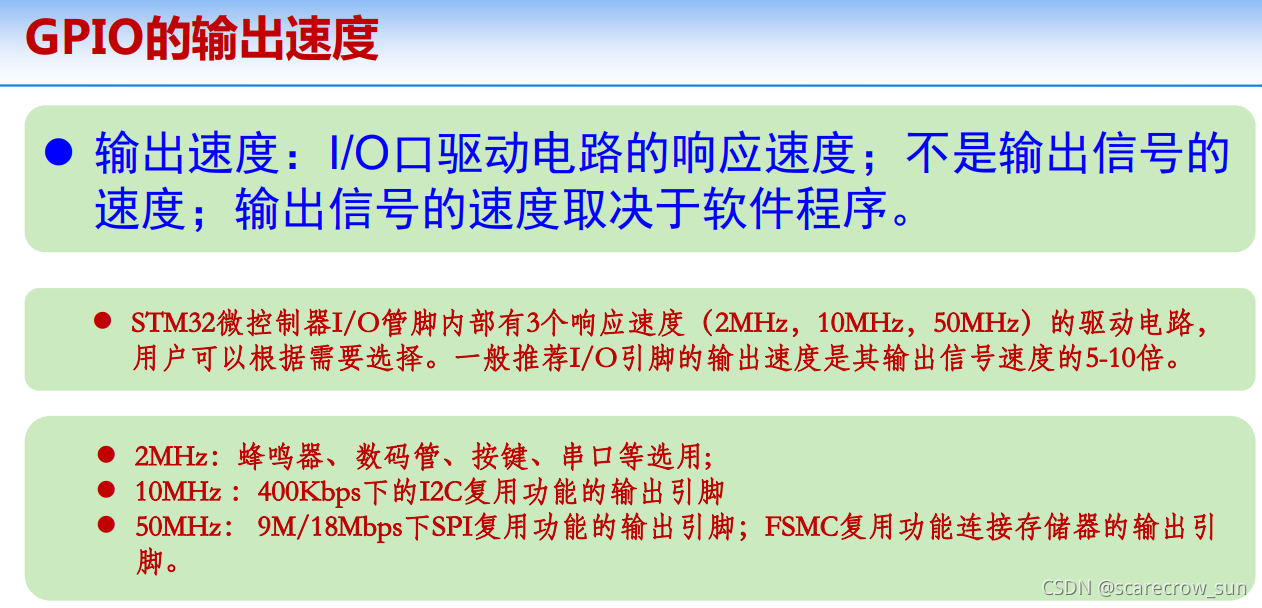

GPIO的输出速率

GPIO还有一个十分重要的概念,也就是响应速度,相应速度是指,当你的电平需要改变的时候,这个改变的时间需要多少。如果你对这个时间要求十分严格,那么一定要使用高输出速率的IO口。反之则反。

登录后可发表评论

点击登录